Patent DE 10 2021 126 108

Method of extending and using a model to simulate an electronic circuit

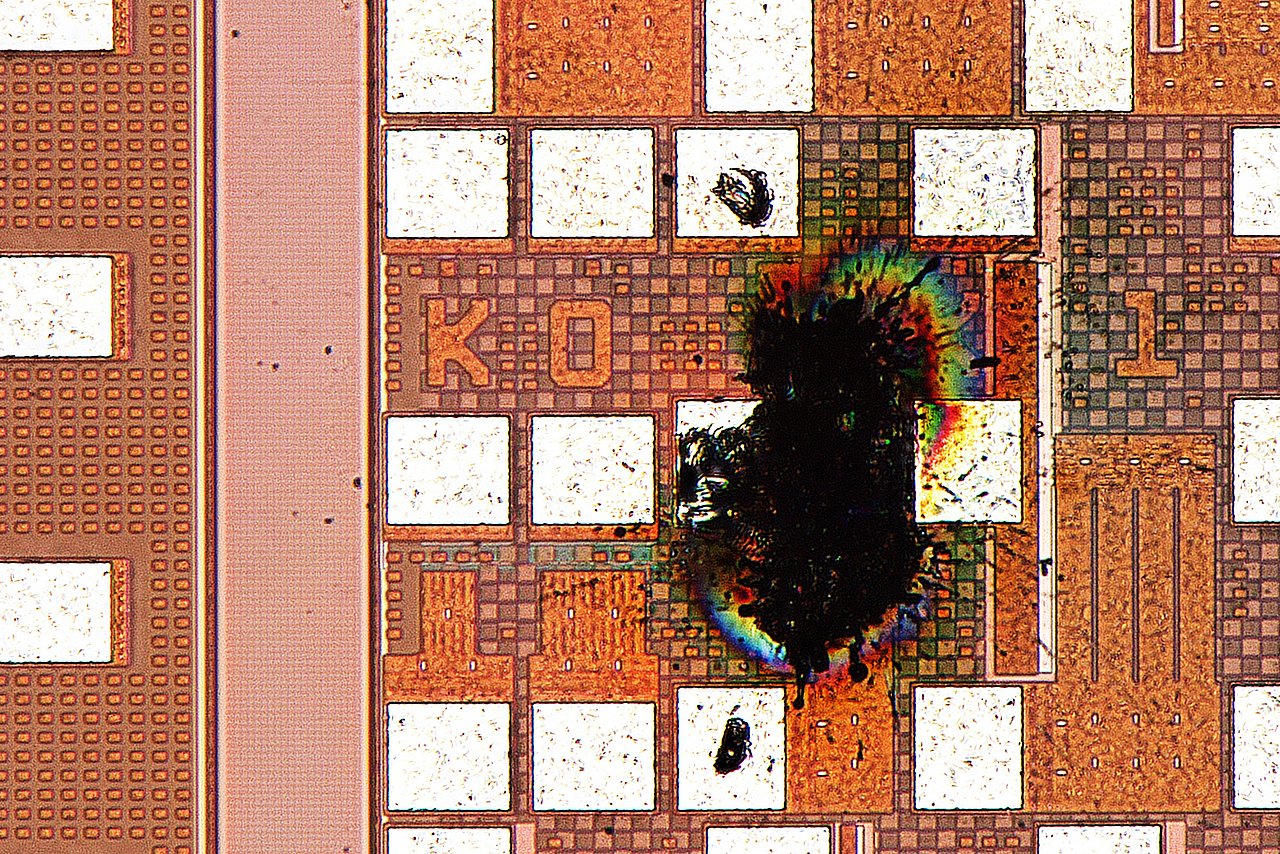

When simulating analogue, digital or analogue-digital circuits on the basis of behavioural models, it is essential how accurately the behavioural models describe the behaviour of the circuit. A model error can lead to a chip design being classified as correct, even though problems are present in the associated circuits and therefore remain undetected. It is therefore important for the user of the behavioural model to know the model error and to be able to adjust the model accuracy and thus increase the reliability of the simulation results.

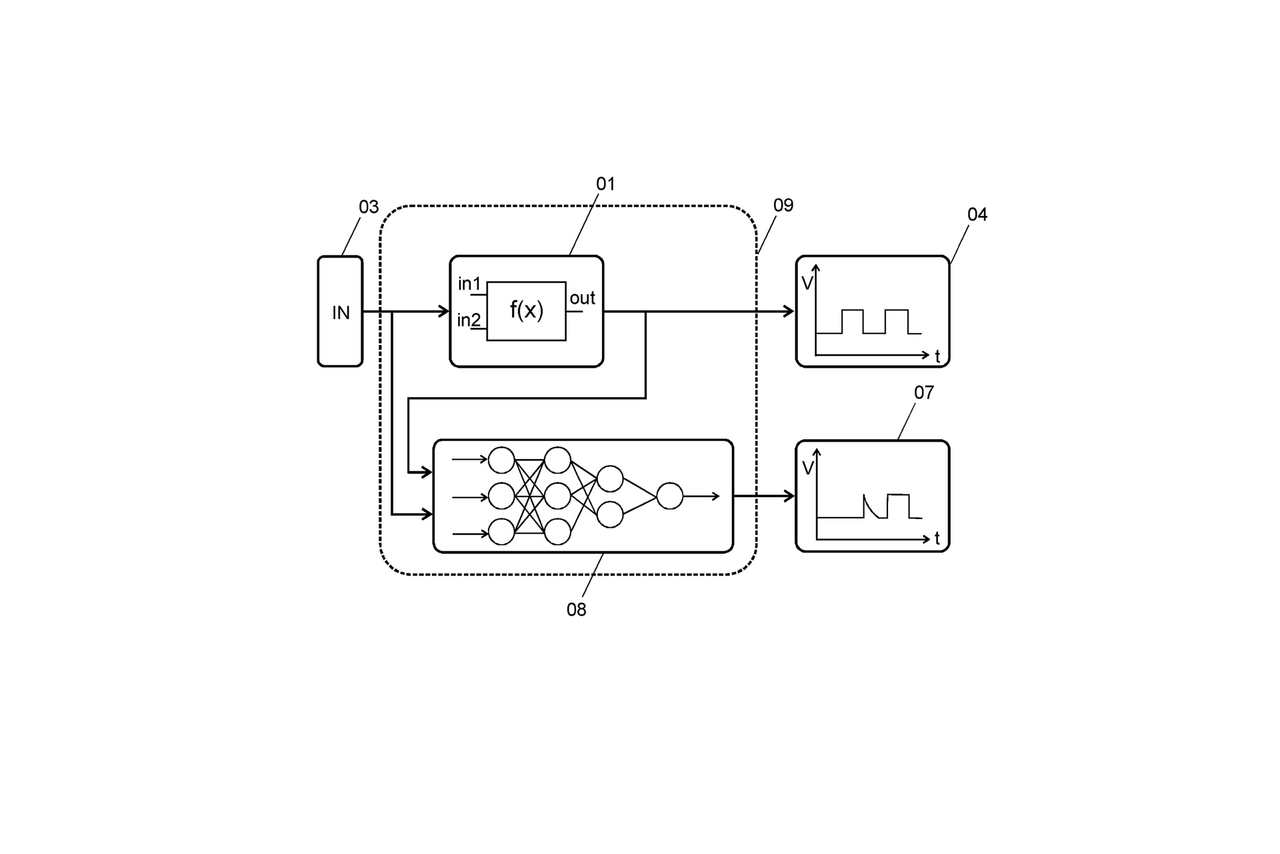

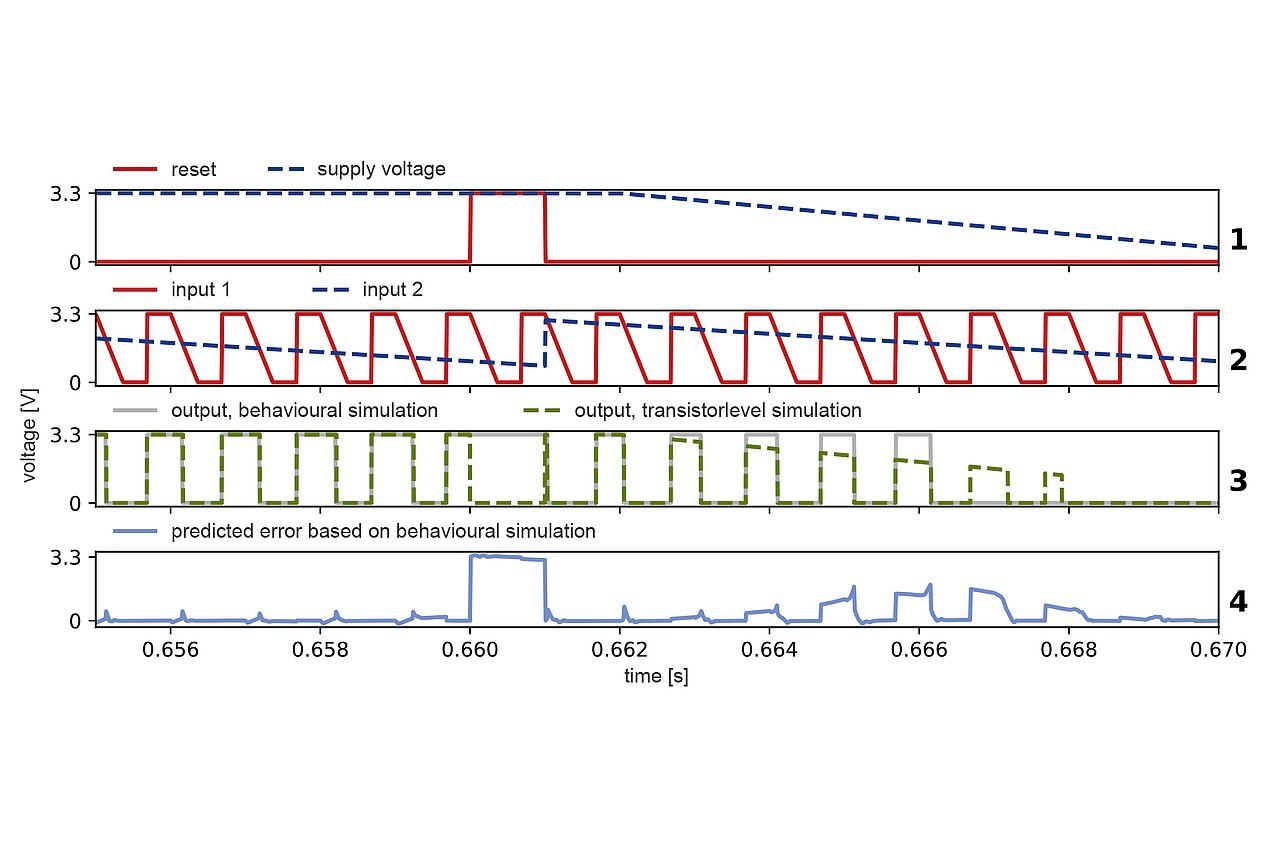

The idea of the invention is an AI-based error estimator that reads the inputs and the output of the behavioural model in parallel to the simulation and estimates the model error based on this. The error can thus be read online. This makes it possible to better estimate the output of the model, react to the error and, for example, change simulation parameters or cancel the simulation.

The model (01) is made up of elements that represent at least groups of semiconductor components of the circuit to be simulated. The model (01) is used in a learning mode to learn an error estimator (08) formed by a machine-learning system by feeding first test signals to inputs of the circuit to be simulated and to corresponding inputs of the model (01) and by comparing at least one resulting output signal of the model (01) with at least one resulting corresponding output signal of the circuit to be simulated. The model (01) is extended by the trained error estimator (08). The model (01) extended by the learnt error estimator (08) is used in a simulation mode for simulating and verifying the electronic circuit.

Patent No.:DE 10 2021 126 108

Inventor:Georg Gläser. Martin Grabmann

Application:

Improved (faster| safer) simulation models for circuit IP/IP blocks (e.g. Memory IP| interface IP etc.)Research field:Integrated sensor systems

published patent application

Application date:08 October 2021

Date of first publication:13 April 2023

Related content

Project

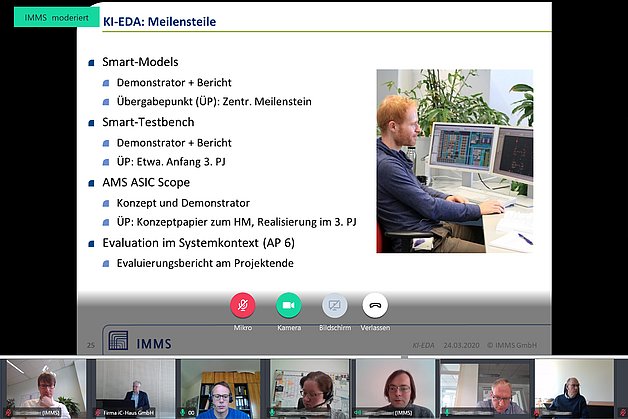

KI-EDA

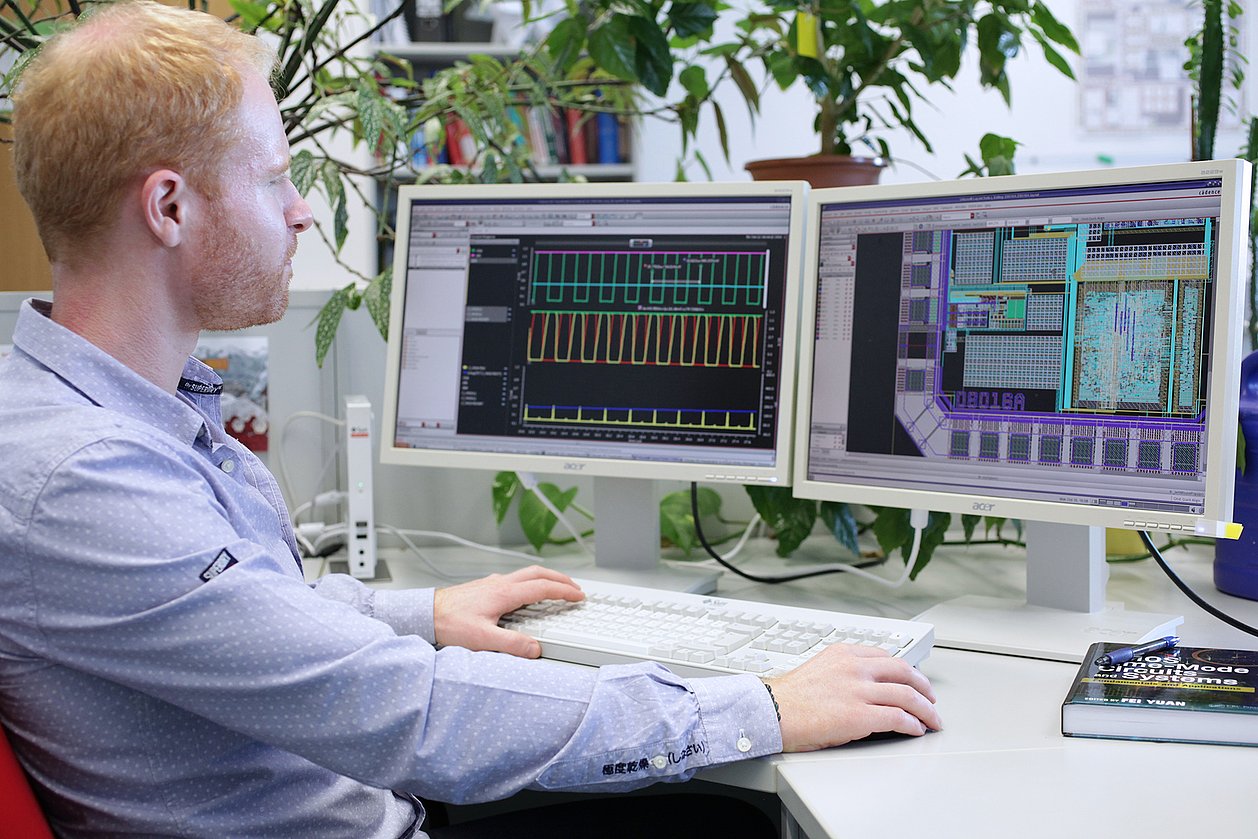

IMMS developed smart models and tes methods for the design of sensor and control chips for I4.0 applications

Press release,

Reliable and faster chip designs through invasive and parametric simulation methods

Dissertation on new methods for automation in integrated circuit design

Press release,

KI zum Entwurf von Antriebssteuerchips als Schlüsselprodukte für die Industrie 4.0

Virtuelles Kick-off-Meeting zum Projektstart von KI-EDA

Testsystem für die Charakerisierung analoger und digitaler Strukturen – Mixed-Signal-Analyse wird mobiltauglich

Tom Reinhold1.Elektronik, 24.2024, 26. November 2024, Seite 70 - 73, ePaper: wfm-publish.blaetterkatalog.de/frontend/mvc/catalog/by-name/ELE

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, Ehrenbergstraße 27, 98693 Ilmenau, Germany.Validierung KI-basierter Simulationsmethoden im Chip-Entwurf, Testbench in Hardware

Tom Reinhold1.Elektronik, 25.2023, 29. November 2023, Seite 60 - 64, ePaper: wfm-publish.blaetterkatalog.de/frontend/mvc/catalog/by-name/ELE

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, 98693 Ilmenau, Germany.Automatisiertes Testen mikroelektronischer Schaltungen – Fuzzing findet Bugs in Hardware

Henning Siemen1. Jonas Lienke1. Georg Gläser1.Elektronik, 21.2023, 18. Oktober 2023, Seite 64 - 67, ePaper: wfm-publish.blaetterkatalog.de/frontend/mvc/catalog/by-name/ELE

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, 98693 Ilmenau, Germany.IC-Entwicklung: Effizientere Simulation mit KI-basierter Modellfehlerschätzung

Henning Siemen1. Martin Grabmann1. Eric Schäfer1. Georg Gläser1.Elektronik, 17-18/2023, 23. August 2023, Seite 66 - 69, ePaper: wfm-publish.blaetterkatalog.de/frontend/mvc/catalog/by-name/ELE

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, 98693 Ilmenau, Germany.

Event,

SMACD 2023

International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design

Event,

SMACD 2022

International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design

Contact

Contact

Eric Schäfer, M. Sc.

Head of Microelectronics / Branch Office Erfurt

eric.schaefer(at)imms.de+49 (0) 361 663 25 35

Eric Schäfer and his team research Integrated sensor systems, especially CMOS-based biosensors, ULP sensor systems and AI-based design and test automation. The results are being incorporated into research on the lead applications Sensor systems for in-vitro diagnostics and RFID sensor technology. It will assist you with services for the development of Integrated circuits and with IC design methods.