Dr.-Ing. Dirk Nuernbergk, Melexis

“The institute has developed and implemented a program that automatically finds and evaluates critical parasitics even at the design stage. In consequence, layout optimisation, which normally takes so long, is massively accelerated. In a very short time, we were able to identify the problematic points in three circuits.”

”We are a company that has supplied ICs to the automotive industry for more than 20 years. Each year, our research and development team works on dozens of new smart ICs and sensor components. These are needed not only for making cars, trucks and agricultural machinery safer, more reliable and energy-efficient but also to underpin systems in industry, medicine and home automation.

Because our ICs contain ever more blocks of smart functionality, they are ever more complex. More and more functions have to be packed compactly onto a chip surface. In these situations, physical effects may arise which have nothing to do with the desired functionality. An example is crosstalk between neighbouring wires, which often makes it necessary to go through numerous costly and time-consuming iterations to optimise the layout. There are standard tools which serve to report errors but are unable to identify which elements are causing those errors, requiring modification. If commercial considerations demand that chip surface area is kept to a minimum and yet at the same time laid out more compactly, it is like squaring of the circle. Depending on the complexity of a particular circuit, the designer may be confronted with the need to modify manually several hundred or even a thousand potential sources of error and investigate the effects of as many individual coupling situations.

IMMS has come up with a solution. The institute has developed and implemented a program that automatically finds and evaluates critical parasitics even at the design stage. In consequence, layout optimisation, which normally takes so long, is massively accelerated. On evaluating this method, we clearly saw its high potential. In a very short time, we were able to identify the problematic points in three circuits. We are looking forward to using the procedure yet again in the future for our circuit designs.“

The reference is related to:

Contact

Contact

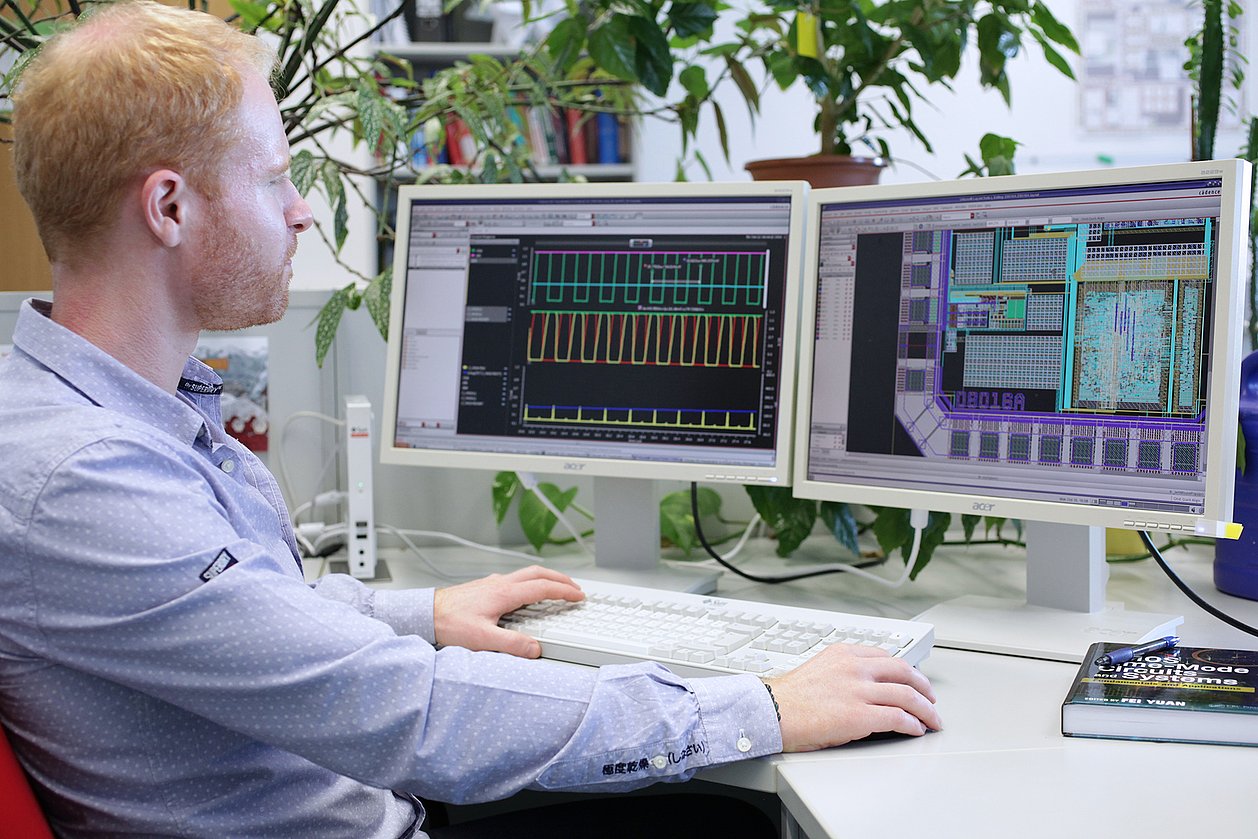

Eric Schäfer, M. Sc.

Head of Microelectronics / Branch Office Erfurt

eric.schaefer(at)imms.de+49 (0) 361 663 25 35

Eric Schäfer and his team research Integrated sensor systems, especially CMOS-based biosensors, ULP sensor systems and AI-based design and test automation. The results are being incorporated into research on the lead applications Sensor systems for in-vitro diagnostics and RFID sensor technology. It will assist you with services for the development of Integrated circuits and with IC design methods.