Patent DE 10 2011 113 421

Method for automatic topology modification in the design of analogue integrated circuits

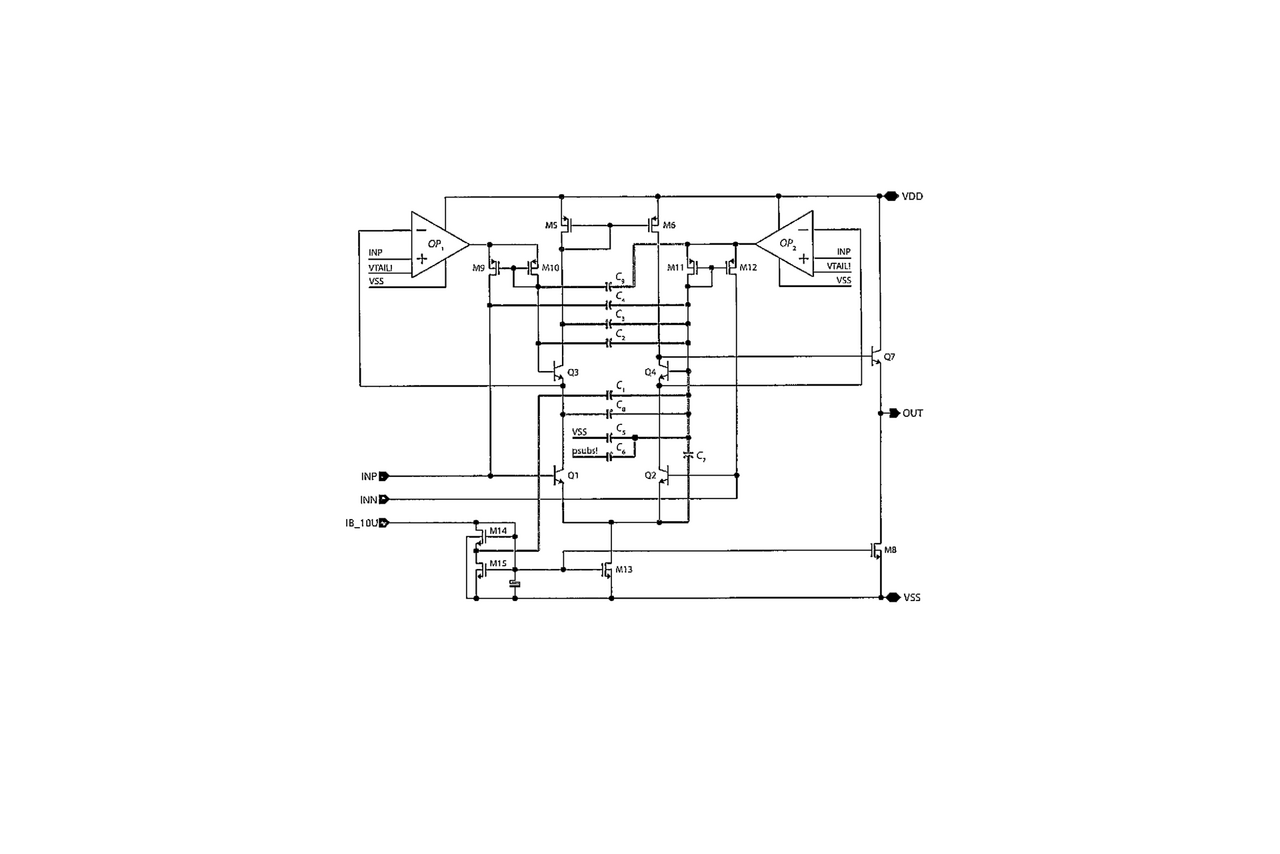

The invention relates to a method for automatic topology modification in the design of analogue, in particular integrated circuits for optimising the transmission behaviour and the stability properties on the basis of systematic eigenvalue shifts with particular consideration of the frequency behaviour and the stability of the respective circuit as well as the pole and zero positions relevant for this.

According to the invention, new network elements, in particular capacitances, are added to the initial circuit design between all independent circuit nodes, whereby the quantity of inserted network elements is weighted and sorted in several steps in order to extract those elements which lead to a permanent improvement in the circuit performance and which are associated with a minimum chip area requirement, whereby a parametric pole-zero analysis is carried out for each inserted network element or a gradient-based eigenvalue optimisation is carried out.

Patent No.:DE 10 2011 113 421

Inventor:Ralf Sommer. Eric Schäfer. Dominik Krauße. Eckhard Hennig

Application:

Integrated circuit design| analogue electronics| amplifier designResearch field:Integrated sensor systems

published patent application

Application date:05 October 2010

Date of first publication:15 March 2012

Contact

Contact

Eric Schäfer, M. Sc.

Head of Microelectronics / Branch Office Erfurt

eric.schaefer(at)imms.de+49 (0) 361 663 25 35

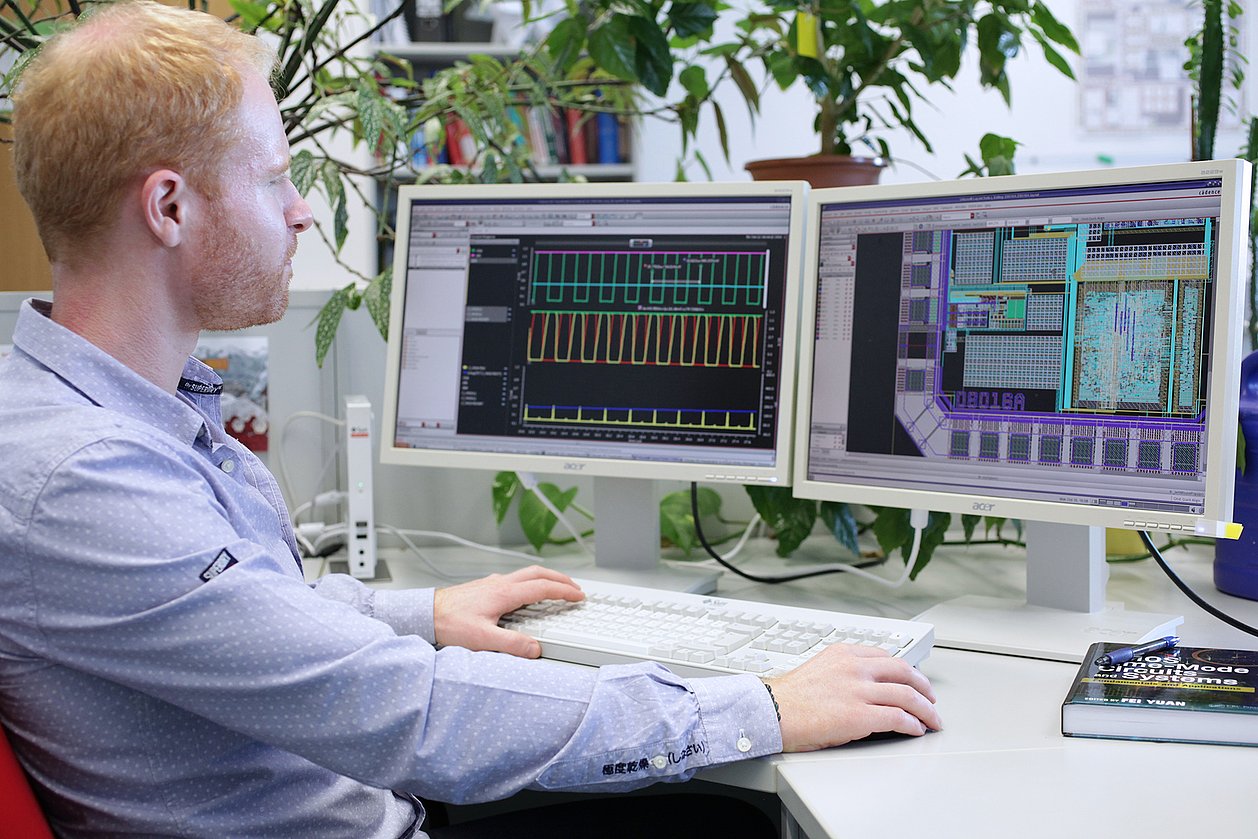

Eric Schäfer and his team research Integrated sensor systems, especially CMOS-based biosensors, ULP sensor systems and AI-based design and test automation. The results are being incorporated into research on the lead applications Sensor systems for in-vitro diagnostics and RFID sensor technology. It will assist you with services for the development of Integrated circuits and with IC design methods.