Projekt VE-VIDES

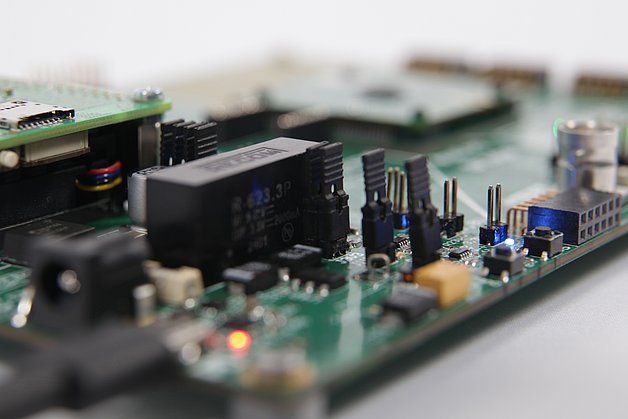

Gegen Hackerangriffe: Innovative Chip-Architekturen, Modellierungs- und Verifikationsmethoden für vertrauenswürdige Elektronik

Hacker greifen bereits heute gezielt vernetzte Fahrzeuge, Maschinen, Industrie- und Telekommunikationsanlagen an, um sich illegal Vorteile zu verschaffen, wie z.B. Wettbewerbern zu schaden, geistiges Eigentum zu stehlen oder sensible Daten zu entwenden.

Gleichzeitig steigt der Bedarf, Automobilsysteme, Unternehmens- und Produktionsnetzwerke funktionaler, komfortabler, verkehrssicherer und energie- sowie kosteneffizienter zu gestalten. Bereits diese Anforderungen lassen die Systeme nicht nur immer komplexer und in ihrer Entwicklung immer anspruchsvoller werden. Sie sind auch immer stärker vernetzt. Mehr Komplexität und mehr Vernetzung bieten auch mehr Möglichkeiten für Angriffe auf diese Systeme, die zudem größere Auswirkungen haben können und somit für Angreifer auch lukrativer sind.

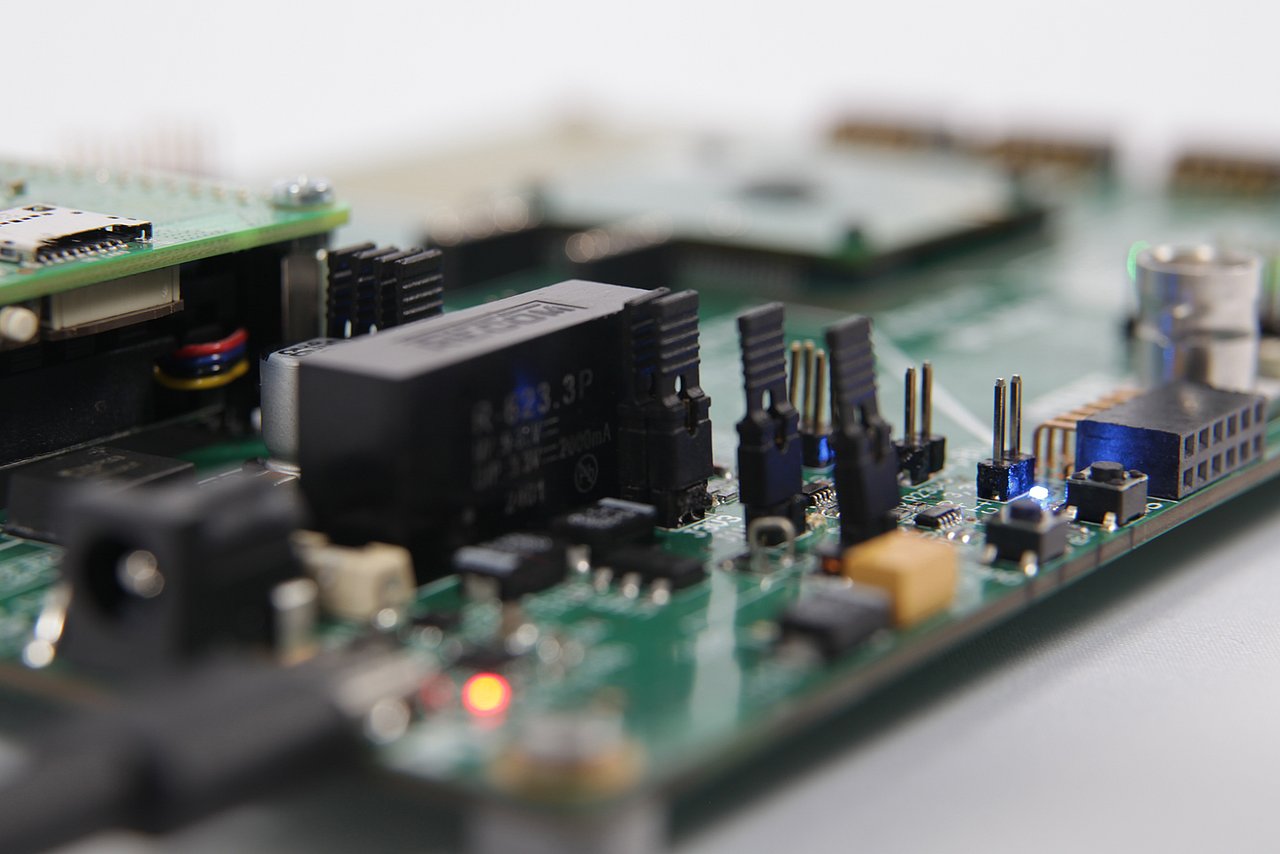

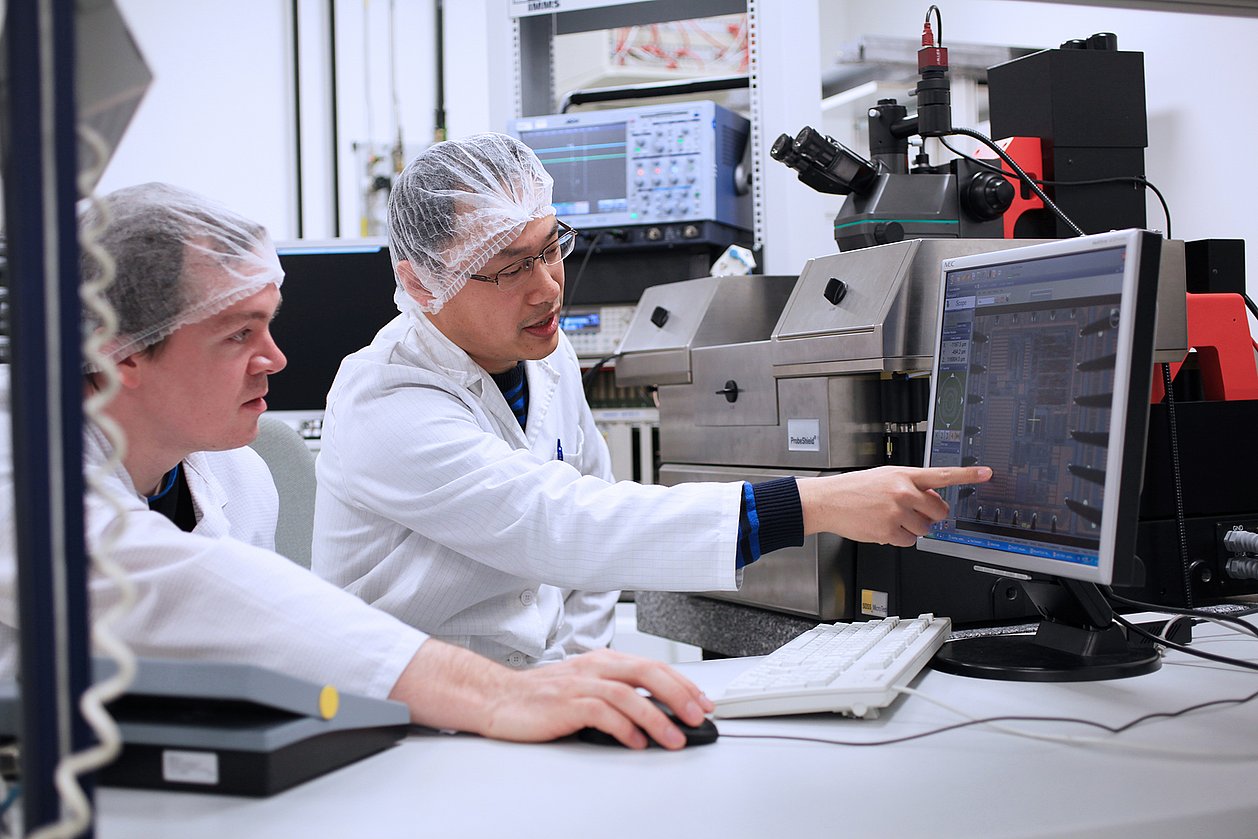

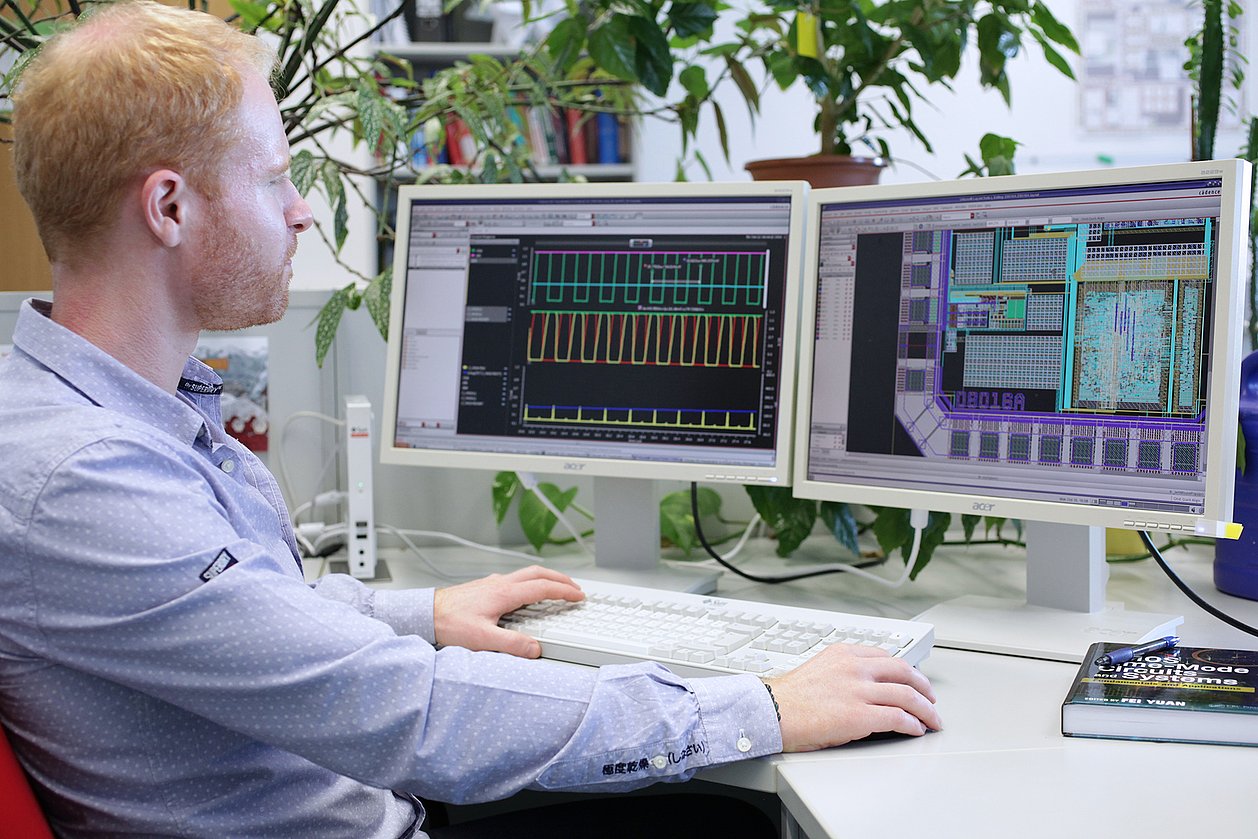

Im Projekt sichert das IMMS mit seinen Partnern den Entwurf von integrierten Systemen durch innovative Chip-Architekturen sowie automatisierte Modellierungs- und Verifikationsmethoden ab. Dadurch soll die Vertrauenswürdigkeit des Systems nicht nur während des Entwurfs, sondern auch im Betrieb laufend überprüft und somit ein Hackerangriff abgewehrt werden können.

Akronym / Name:

VE-VIDES / Designmethoden und HW/SW-Co-Verifikation für die eindeutige ldentifizierbarkeit von ElektronikkomponentenLaufzeit:2021 – 2024

Anwendung:

|IC-Entwurf| Chip-Design| Entwurfsmethodik| KI| Modelle| Modellierung| Design SupportForschungsfeld:Integrierte Sensorsysteme

Zugehörige Inhalte

Referenz

Mirjam Mantel, Siemens AG

„Die enge Kooperation mit dem IMMS war geprägt von einer praxisnahen und anwendungsorientierten Herangehensweise. Die Partnerschaft hat unsere Erwartungen übertroffen und wir schätzen die Ergebnisse als sehr erfolgreich ein.“

Trust is Good, Monitoring is Better: FPGA- & TEE-Based Monitoring for Malware-Detection

Friederike Bruns1. Georg Gläser2. Florian Kögler2. Jonas Lienke2. Nithin R. Nanjundaswamy3. Gregor Nitsche3. Behnam R. Perjikolaei4. Jörg Walter4.13th IMA International Conference on Modelling in Industrial Maintenance and Reliability MIMAR2025, July 8-10, 2025, Université de Lorraine, France, DOI: doi.org/10.19124/ima.2025.01.25

1Carl von Ossietzky Universität Oldenburg, Oldenburg, Germany. 2IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH (IMMS GmbH), Ehrenbergstraße 27, 98693 Ilmenau, Germany. 3DLR Institut für Systems Engineering, Oldenburg, Germany. 4OFFIS e.V. Institut für Informatik, Oldenburg, Germany.Propagation Delay Estimation for Mixed-Signal Modeling of Comparators

Martin Grabmann1. Eric Schäfer1. Georg Gläser1.2024 20th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Volos, Greece, July 02-05, 2024, pp. 1-4, DOI: doi.org/10.1109/SMACD61181.2024.10745467

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, Ehrenbergstraße 27, 98693 Ilmenau, Germany.Trust is good, monitoring is better: An FPGA/TEE-Based Monitoring-Approach to Malware Detection and Prevention

Friederike Bruns1. Georg Gläser2. Florian Kögler2. Jonas Lienke2. Nithin Ravani Nanjundaswamy3. Gregor Nitsche3. Behnam Razi Perjikolaei1. Jörg Walter1.edaWorkshop 2024 and the European Nanoelectronics Applications, Design & Technology Conference (ADTC), 9. - 10. April 2024, Dresden, Germany

1OFFIS e.V. Institut für Informatik Oldenburg. 2IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, Ehrenbergstraße 27, 98693 Ilmenau, Germany. 3DLR Institut für Systems Engineering für zukünftige Mobilität.Hot Fuzz: Assisting verification by fuzz testing microelectronic hardware

Henning Siemen1. Jonas Lienke1. Georg Gläser1.2023 19th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Funchal, Portugal, July 03-05, 2023, pp. 1-4, DOI: doi.org/10.1109/SMACD58065.2023.10192176

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, 98693 Ilmenau, Germany.

Pressemitteilung,

Zuverlässige und schnellere Chip-Designs durch invasive und parametrische Simulationsmethoden

Dissertation zu neuen Methoden für die Automatisierung beim Entwurf integrierter Schaltungen

Veranstaltung,

MIMAR 2025

International Conference on Modelling in Industrial Maintenance and Reliability

Veranstaltung,

SMACD 2024

International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD)

Veranstaltung,

edaWorkshop 2024

edaWorkshop24 and the European Nanoelectronics Applications, Design & Technology Conference (ADTC)

Veranstaltung,

CiS-Workshop 2023

Workshop Simulation & Design 2023 am CiS Forschungsinstitut für Mikrosensorik

Kontakt

Kontakt

Eric Schäfer, M. Sc.

Leiter Mikroelektronik und Institutsteil Erfurt

eric.schaefer(at)imms.de+49 (0) 361 663 25 35

Eric Schäfer und sein Team erforschen Integrierte Sensorsysteme und hier insbesondere CMOS-basierte Biosensoren, ULP-Sensorsysteme und KI-basierte Entwurfs- und Testautomatisierung. Die Ergebnisse fließen in die Forschung an den Leitthemen Sensorsysteme für die In-vitro-Diagnostik und RFID-Sensoren ein. Er unterstützt Sie mit Dienstleistungen rund um die Entwicklung integrierter Schaltungen und mit KI-basierten Methoden für komplexe IC-Entwürfe.

Förderung

Das Verbundprojekt VE-VIDES wurde vom Bundesministerium für Forschung, Technologie und Raumfahrt (BMFTR) unter dem Kennzeichen 16ME0246 gefördert.