Presseinformationen

IMMS ”Competition Runner-up“ für Methodik zur Design-Automation

Verlässliche und automatisierte Verifikation von Chip-Designs beschleunigt Entwicklungszeiten

Ilmenau, 22.06.2017. Das IMMS wurde gemeinsam mit Forschungspartnern auf der Konferenz ”14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design“ (SMACD 2017) als ”Competition Runner-up“ für den Beitrag ”Automated Generation of System-Level AMS Operating Condition Checks: Your Model’s Insurance Policy“ ausgezeichnet.

Die Arbeit wurde im Clusterforschungsprojekt ANCONA (Analog-Coverage in der Nanoelektronik) entwickelt. Gemeinsam mit fünf Universitäten und Forschungseinrichtungen erarbeitet das IMMS in ANCONA rechnergestützte Verifikationsmethoden, die den Entwurf analog/digitaler Schaltungen erleichtern und deutlich beschleunigen sollen. Solche Schaltungen sind die technologische Basis für das „Internet der Dinge“ und „Industrie 4.0“. Das Zusammenspiel von hierfür neu entwickelten Systemkomponenten und deren parasitären Interaktionen kann bislang meist erst im Versuchsaufbau getestet werden. Daher erarbeiten die Projektpartner rechnergestützte Verfahren, um die korrekte Funktion der komplexen Systeme schon während des Entwurfs zuverlässig nachzuweisen.

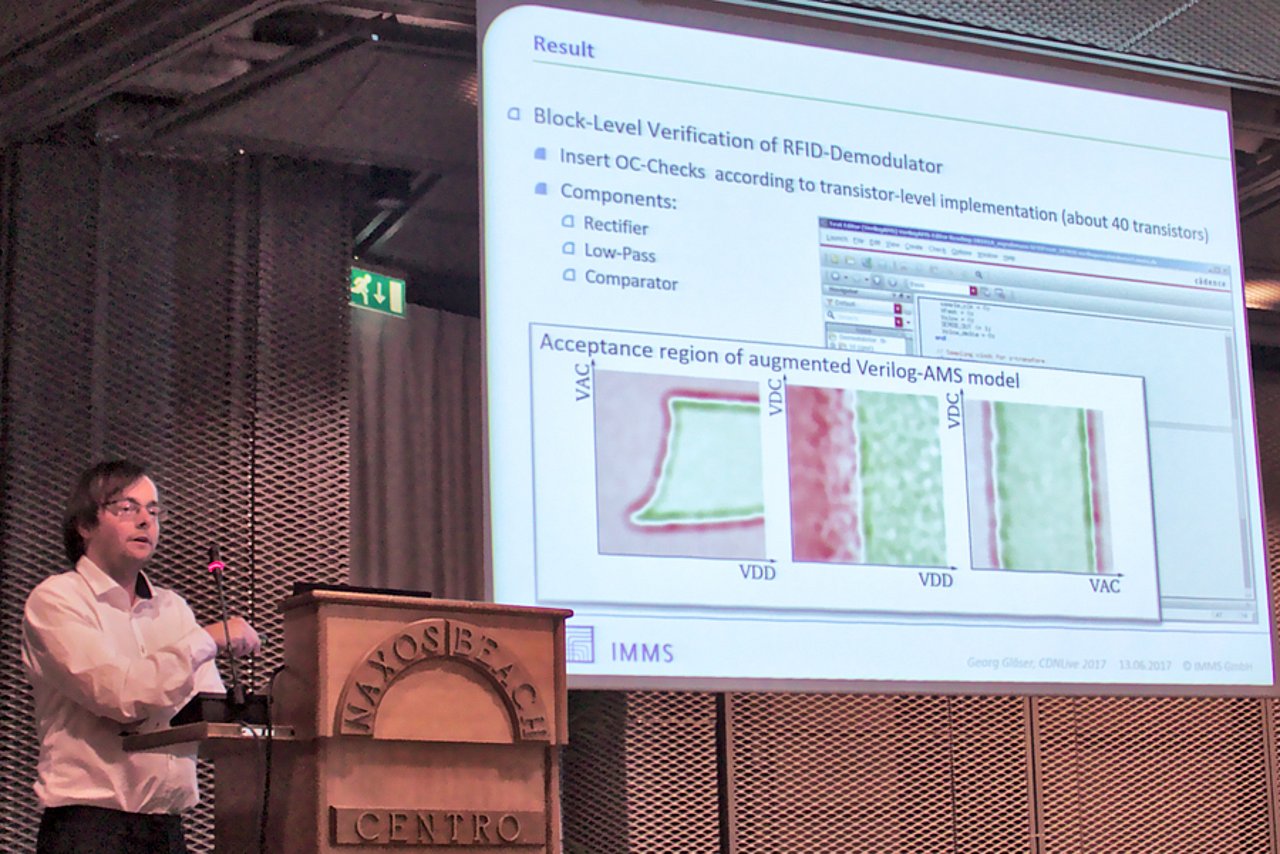

Im genannten Beitrag wurde eine Methode vorgestellt, mit denen Modelle für gemischt analog/digitale Schaltungsblöcke automatisch durch Prüfbedingungen erweitert werden. Mit diesen Prüfbedingungen wird sichergestellt, dass das Modell ein abgesichertes Verifikationsergebnis garantiert. Bislang konnte es vorkommen, dass sich eine positive Verifikation eines Entwurfs mit rein funktionalen Modellen als falsch herausstellte und durch zusätzliche Simulationen abgesichert werden musste. Durch die im neuen Ansatz vorgenommene Erweiterung um Prüfbedingungen wird die Wahrscheinlichkeit einer solchen falsch-positiven Verifikation stark verringert: Ursachen für Falschaussagen sind nahezu eliminiert.

Bisher sind derartige Prüfbedingungen (Operating Condition Checks) nur für Transistorschaltungen verfügbar. Eine Simulation/Verifikation eines größeren Systems ist damit mit sehr hohem Aufwand verbunden. Deshalb werden üblicherweise Modelle für einzelne Komponenten verwendet. Diese Modelle müssen dabei nicht nur in ihrer Funktion der Schaltung entsprechen, sondern auch die Umgebungsbedingungen wie z.B. Versorgungsspannung, Eingangssignalamplitude und Temperatur einbeziehen. Bisher ist das nur über komplexe Ausdrücke möglich, die manuell im Modell ergänzt werden müssen – was neben dem Implementationsaufwand den Verifikationsaufwand steigert. Die vorgestellte Methode automatisiert diesen Prozess weitgehend. Der Benutzer gibt in einer Simulation der Schaltung Parameter für relevante Betriebsbedingungen an, woraufhin diese durch einen Explorationsalgorithmus untersucht werden. Das Ergebnis wird automatisch in das Verilog-AMS-Modell der Schaltung integriert und kann direkt in der weiteren Verifikation verwendet werden.

Das IMMS hat diese neuen Methoden zur elektronischen Designautomation (EDA) direkt in den Verifikationsprozess für eine Chip-Entwicklung im parallel am IMMS bearbeiteten F&E-Projekt ADMONT verwendet. Auch die Ergebnisse dieser ersten Beispiel-Verifikation wurden in dem Beitrag präsentiert.

Georg Gläser1. Martin Grabmann1. Gerrit Kropp1. Andreas Fürtig2.

14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design, 12th–15th June 2017, Giardini Naxos – Taormina, Italy, 15.06.2017

1IMMS Institut für Mikroelekronik- und Mechatronik-Systeme gemeinnützige GmbH, Ehrenbergstraße 27, D-98693 Ilmenau, Germany. 2Institute for Computer Science, Goethe Universität Frankfurt a. M., Germany.

Zugehörige Inhalte

Projekt

ANCONA

Die erarbeiteten rechnergestützten Verifikationsmethoden beschleunigen die Entwicklung von Industrie-4.0-Anwendungen.

Veranstaltung,

DDECS 2019

IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems

Veranstaltung,

edaBarCamp -- may the 4th be with you!

Originating from our PhD meetings in a german research project, we gained the idea of starting an open research meeting based on the barcamp-concept.

Veranstaltung,

SMACD 2018

Vortrag auf der 15th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design

Kontakt

Kontakt

Dipl.-Hdl. Dipl.-Des. Beate Hövelmans

Leiterin Unternehmenskommunikation

beate.hoevelmans(at)imms.de+49 (0) 3677 874 93 13

Beate Hövelmans ist verantwortlich für die Text- und Bildredaktion dieser Webseite, für die Social-Media-Präsenz des IMMS auf LinkedIn und YouTube, die Jahresberichte, für die Pressearbeit mit Regional- und Fachmedien und weitere Kommunikationsformate des IMMS. Sie stellt Ihnen Texte, Bilder und Videomaterial für Ihre Berichterstattung zum IMMS bereit, vermittelt Kontakte für Interviews und ist Ansprechpartnerin für Veranstaltungen.