Projekt VE-ARiS

Das IMMS entwickelte Verfahren zum Kopierschutz für integrierte Schaltungen, um das Know-how von Partnern zu sichern.

Fälschungen und Kopien als Risiko für sicherheitskritische Systeme und wirtschaftliche Substanz

Kopierte Chips sind ein Problem für Hersteller und Anwender. Die Hersteller oder Design-Häuser entwerfen mit viel Know-how und hohem finanziellen Einsatz innovative Chips und erleiden mit jeder Kopie dieser Chips einen wirtschaftlichen Schaden. Anwender können sich bei Kopien nicht auf die Leistungsparameter der Originale verlassen und riskieren damit potenziell die Sicherheit ihrer eigenen Produkte.

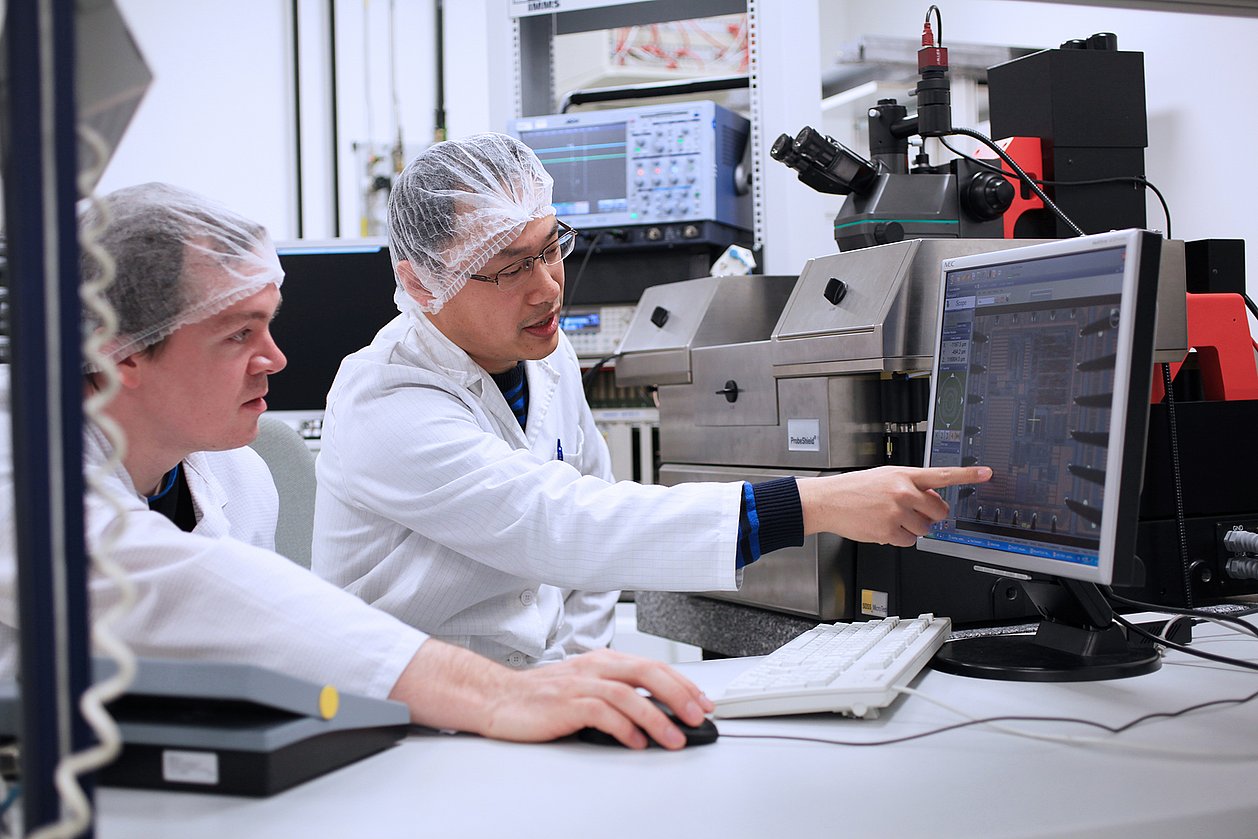

Die Kopien entstehen auf verschiedene Arten: Ein Chip kann anhand des Datenblatts „nachgebaut“ werden, es entsteht also ein neues Chip-Design mit annähernd gleichen Eigenschaften. Sollen die Schaltungen selbst imitiert werden, werden die Chips oft mit verschiedenen Methoden untersucht, um den inneren Aufbau zu rekonstruieren. Zum Teil werden die Chips in kleinen Schritten abgeschliffen und unter dem Mikroskop fotografiert und anhand dieser Bilder die zur Fertigung benötigten Layouts nachgezeichnet.

Methoden an Systemen der Industriepartner validiert

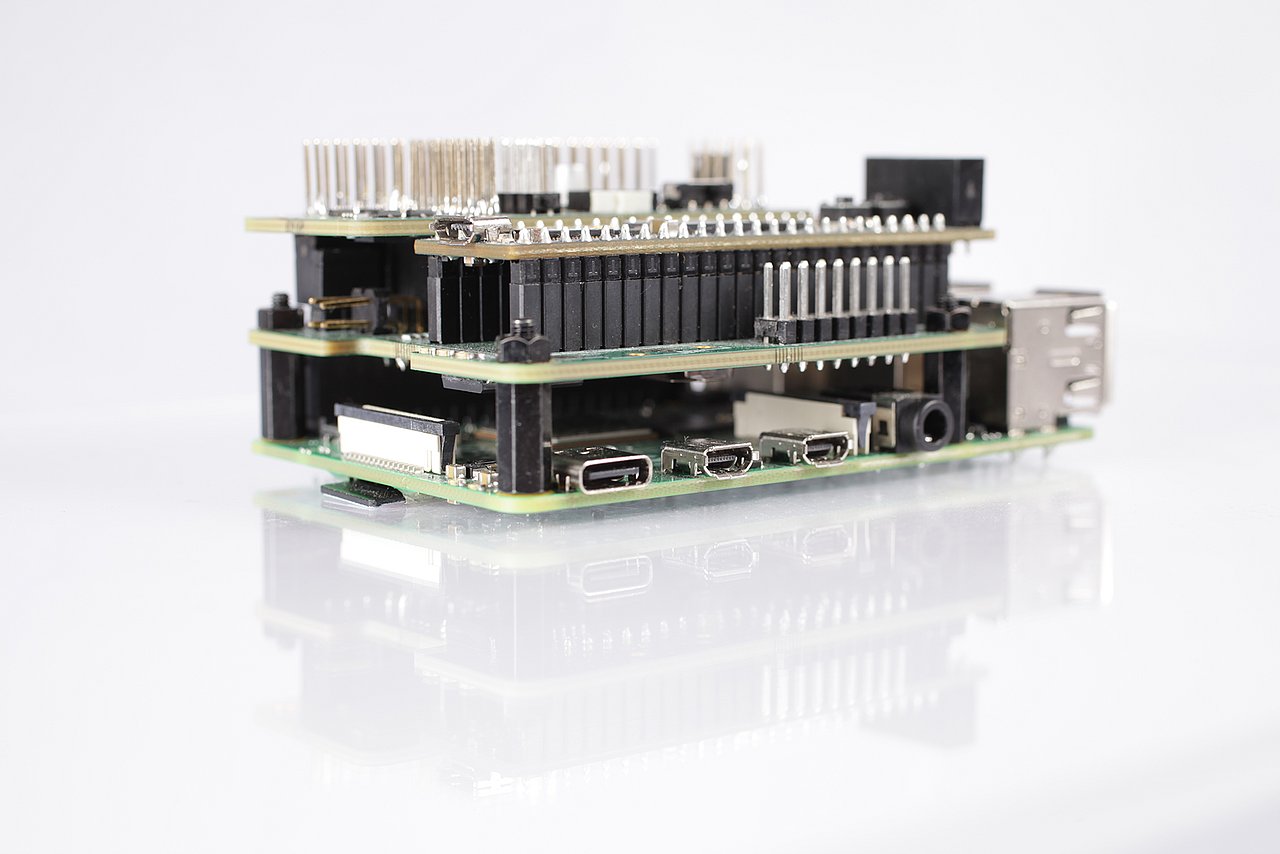

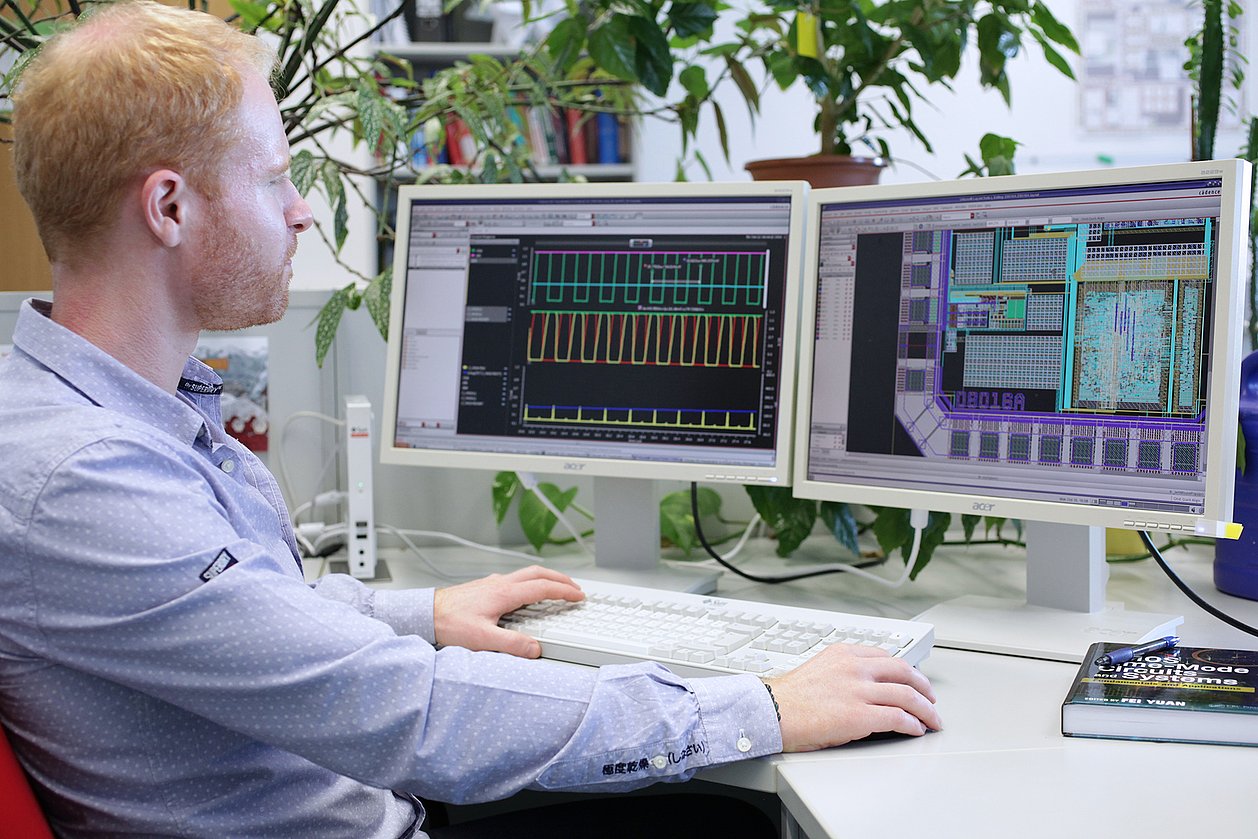

Im Projekt ARiS hat das IMMS Methoden erforscht, dieses Kopieren schwerer zu machen und somit Chips davor zu schützen. Dabei wurden zwei Forschungsrichtungen verfolgt: Gegen das Nachbauen wurde ein Wasserzeichen untersucht, mit dem originale Chips markiert werden können. Wie bei Geldscheinen wird so ein Check eingebaut, mit dem ein Original identifiziert werden kann. Angriffe, wie das Abschleifen von Chips, standen ebenfalls im Fokus der Arbeiten. Am IMMS wurde ein Machine-Learning-basiertes Angriffsmodell entwickelt, mit dem dieser Reverse-Engineering-Prozess simuliert werden kann. Auf dieser Basis können Schaltungsteile gefunden werden, die leicht kopierbar sind und die im nächsten Schritt „gehärtet“ werden können. Hierbei werden Strukturen verwendet, die nur schwer rückerkannt werden können. Die untersuchten Ansätze zum Kopierschutz wurden anhand verschiedener Demonstratoren erfolgreich validiert.

.

Akronym / Name:

VE-ARiS / Verbundprojekt: Elektronischer Knowhow-Schutz für innovative Sensorsysteme – ARiSLaufzeit:2021 – 2024

Anwendung:

|IC-Entwurf| Chip-Design| Entwurfsmethodik| KI| Machine Learning| Maschinelles Lernen| Modelle| Modellierung| Design SupportForschungsfeld:Integrierte Sensorsysteme

Zugehörige Inhalte

Referenz

Dr. Heiner Flocke, iC-Haus GmbH

„Durch den Austausch von Know-how und Ressourcen konnten wir gemeinsam eine Lösung entwickeln, die gestellte Vorgaben erfüllte und sogar übertroffen hat.“

VE-ARiS: Alberich und die Tarnkappenfabrik. SKAW – Schaltungskopierbarkeitsanalysewerkzeug

Adrian Pitterling1. Florian Kögler1. Georg Gläser1.Tage der vertrauenswürdigen Elektronik 2024, 4. - 5. Juni 2024, München

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, Ehrenbergstraße 27, 98693 Ilmenau, Germany.VE-ARiS: Elektronischer Knowhow-Schutz für innovative Sensorsysteme. Abwehr von Reserve-Engineering auf IC-Ebene

Projektkonsortium VE-ARiS (iC-Haus GmbH. Wachendorff Automation GmbH & Co. KG. IMMS GmbH).Tage der vertrauenswürdigen Elektronik 2024, 4. - 5. Juni 2024, München

VE-ARiS – „Alberich“ – Machine-Learning-basierte Vorhersage der Kopierbarkeit von ASICs

Florian Kögler1.Digitale Fachkonferenz „Vertrauenswürdige Elektronik 2022“, 9. - 10. März 2022, online

1IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH, 98693 Ilmenau, Germany.

Pressemitteilung,

Zuverlässige und schnellere Chip-Designs durch invasive und parametrische Simulationsmethoden

Dissertation zu neuen Methoden für die Automatisierung beim Entwurf integrierter Schaltungen

Pressemitteilung,

Elektronischer Knowhow-Schutz für innovative Sensorsysteme

iC-Haus, IMMS und Wachendorff starten BMBF-Verbundprojekt VE-ARiS

Veranstaltung,

Tage der vertrauenswürdigen Elektronik 2024

Ergebnispräsentationen der Forschungsprojekte der Förderrichtlinien für vertrauenswürdige Elektronik (ZEUS) und zukunftsfähige Spezialprozessoren und Entwicklungsplattformen (ZuSE) des Bundesministeriums für Bildung und Forschung (BMBF)

Veranstaltung,

Vertrauenswürdige Elektronik 2022

Digitale Fachkonferenz des Bundesministeriums für Bildung und Forschung (BMBF)

Kontakt

Kontakt

Eric Schäfer, M. Sc.

Leiter Mikroelektronik und Institutsteil Erfurt

eric.schaefer(at)imms.de+49 (0) 361 663 25 35

Eric Schäfer und sein Team erforschen Integrierte Sensorsysteme und hier insbesondere CMOS-basierte Biosensoren, ULP-Sensorsysteme und KI-basierte Entwurfs- und Testautomatisierung. Die Ergebnisse fließen in die Forschung an den Leitthemen Sensorsysteme für die In-vitro-Diagnostik und RFID-Sensoren ein. Er unterstützt Sie mit Dienstleistungen rund um die Entwicklung integrierter Schaltungen und mit KI-basierten Methoden für komplexe IC-Entwürfe.

Förderung

Das Projekt VE-ARiS wurde durch das Bundesministerium für Forschung, Technologie und Raumfahrt (BMFTR) unter dem Kennzeichen 16ME0242 gefördert.