Presseinformationen

EDA Achievement Award 2018 für Methoden des IMMS zum Entwurf integrierter Schaltungen

Neue Methoden ermöglichen schnelle und fehlerfreie Entwürfe komplexer Industrie-4.0-Lösungen

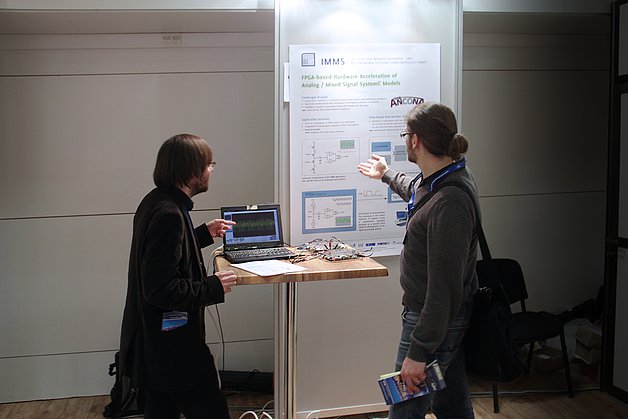

Hannover/Ilmenau, 17.05.2018. Ein Forscher des IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH wurde heute vom edacentrum e.V. zum edaWorkshop18 in Hannover für seine Arbeiten zu neuen Methoden für schnelle und fehlerfreie Entwürfe komplexer integrierter Schaltungen für Industrie-4.0-Lösungen mit dem „EDA Achievement Award 2018“ für besondere Forschungs- und Entwicklungsleistungen für die elektronische Designautomation (EDA) ausgezeichnet. Die prämierten industrienahen und anwendungsorientierten Methoden zur automatisierten Analyse von gemischt analog/digitalen integrierten Schaltungen hatte Georg Gläser im 2017 abgeschlossenen BMBF-Forschungsprojekt ANCONA erarbeitet. Im Mittelpunkt standen die Absicherung und automatisierte Erweiterung von Modellen, das Analysieren der Schwachpunkte von Schaltungen und das Extrahieren von Layout-Beschränkungen. Die Methode besteht aus derzeit drei Komponenten und wurde für Forschungs- und Industrieentwicklungen bereits erfolgreich eingesetzt.

Komplexe Chips müssen automatisiert verifiziert und vor der Fertigung auf ihre Zuverlässigkeit geprüft werden

Designfehler in integrierten Schaltungen können Umsatzeinbußen von mehreren hundert Mio. Dollar durch Produktionsausfälle verursachen und darüber hinaus weitaus höhere Kosten für Rückrufe, Reparaturen und Ersatzleistungen nach sich ziehen. Daher ist man seit jeher bestrebt, Designfehler möglichst früh im Entwurfsprozess festzustellen und derartige Risiken zu minimieren.

„Es müssen immer mehr Funktionen immer kompakter auf einer gegebenen Chip-Fläche angeordnet werden. Dadurch kann es zu physikalischen Effekten kommen, die nicht mit der gewünschten Funktion zusammenhängen, wie z.B. das Übersprechen durch nebeneinanderliegende Leitungen,“ so Dr. Dirk Nuernbergk, Analog Designer, Melexis GmbH Erfurt. Chip-Layouts müssen daher oft in vielen Schritten mit viel Aufwand optimiert werden. Standard-Werkzeuge melden zwar Fehler, können aber nicht die Elemente identifizieren, die Fehler verursachen und verändert werden müssen. „Will man aus wirtschaftlichen Überlegungen Chip-Flächen minimieren und dort gleichzeitig kompaktere Layouts unterbringen, würde das für einen Designer bedeuten, mehrere hundert bis tausend potentielle Fehlerquellen manuell modifizieren und Auswirkungen einzelner Kopplungen untersuchen zu müssen.“

Projekt ANCONA: Rechnergestützte Verfahren weisen korrekte Funktion von Schaltungen schon während des Entwurfs zuverlässig nach

Für die neuen Anforderungen im Industrie-4.0-Kontext sollen intelligentere und damit komplexere Systeme entstehen. Für diese werden künftig zahlreiche neue Systemkomponenten erforscht und entwickelt, deren Zusammenspiel mit den gängigen Methoden meist erst im Versuchsaufbau getestet werden kann. Daher haben die Projektpartner in ANCONA rechnergestützte Verfahren erarbeitet, um die korrekte Funktion dieser Systeme schon während des Entwurfs zuverlässig nachzuweisen. Das soll künftig das Design integrierter Schaltungen erleichtern und deutlich beschleunigen, somit Innovationspotentiale heben und zu Wettbewerbsvorteilen verhelfen.

Prämierte Methode besteht aus derzeit drei Komponenten

Der Entwurf integrierter Schaltungen beginnt meist auf Systemebene, auf der Funktionsblöcke kombiniert werden. In diesen Komponenten werden Schaltungen erstellt, die die gewünschte Funktion realisieren, wie z.B. eine Verstärkung. Nach diesem Entwurfsschritt werden die Funktionalität und die elektrischen Eigenschaften dieser Blöcke in Simulationen verifiziert. Ist dieser Schritt erfolgreich, so wird ein Layout erstellt, das der Bauplan für den Chiphersteller ist: Hier werden die Bauelemente, wie z.B. Transistoren und Widerstände, platziert und mittels Metallleitungen miteinander verbunden.

Komponenten Eins und Zwei: Parasitic-Impact-Analyse und Symmetrieanalyse

Durch die Anordnung der Bauelemente im Layout kann es jedoch zu neuen Effekten kommen, wie z.B. zum Übersprechen durch nebeneinanderliegende Leitungen, was durch parasitäre Kapazitäten verursacht wird. Aufgrund solcher physikalischen Effekte, die nicht mit der gewünschten Funktion zusammenhängen, muss die Schaltung erneut verifiziert werden. Meist führen die Effekte dazu, dass das Layout in weiteren Schritten optimiert werden muss. Hier sind die „Parasitic-Impact-Analyse“ und die „Symmetrieanalyse“ hilfreich: Mit der Symmetrieanalyse können Optimierungspotentiale schon vor dem eigentlichen Layout aufgezeigt werden. Mit der Impact-Analyse werden vorhandene Layouts betrachtet, um einen vielversprechenden Angriffspunkt für die Verbesserungen zu bestimmen. Der aufwendige Prozess der Layout-Optimierung kann so stark verkürzt werden.

Komponente Drei: Automatische Berücksichtigung von Betriebsbedingungen

Nachdem die korrekte Funktion sichergestellt wurde, kann das System schrittweise in immer größeren Funktionsgruppen geprüft werden. Wenn dabei neben der Funktionalität auch die Betriebsbedingungen überwacht werden sollen, ist meist eine sehr detailtreue Simulation auf niedriger Abstraktionsebene notwendig, d.h. mit aufwendigen und zeitintensiven Lösungsverfahren. An dieser Stelle setzt die dritte Methode an: Mit dieser werden Informationen über erlaubte Betriebsbedingungen einzelner Funktionsblöcke automatisch extrahiert. Diese Informationen werden dann in abstraktere Modelle eingearbeitet, mit denen Simulationen stark beschleunigt und gleichzeitig die Betriebsbedingungen abgesichert werden.

Methoden erfolgreich für Forschungs- und Industrieentwicklungen eingesetzt

Schnelle Layout-Optimierungen und zuverlässige Simulationen sind bereits in die Entwicklung von Schaltungen eingeflossen in den Forschungsprojekten HoTSens, EROLEDT, RoMulus und ADMONT und darüber hinaus in Industrieprojekte: „Das IMMS hat eine neue Methode entwickelt und in einem Programm implementiert, das automatisch kritische parasitäre Elemente beim Schaltungsentwurf findet und bewertet. Die zeitaufwendige Layout-Optimierung kann so stark beschleunigt werden,“ so Dr. Dirk Nuernbergk, Melexis GmbH Erfurt. „Eine Evaluation dieser Methode machte das hohe Potential deutlich: Wir konnten in kürzester Zeit die Problemstellen dreier Schaltungen identifizieren. Wir gratulieren zum EDA Achievement Award 2018 und freuen uns darauf, das neue Vorgehen auch zukünftig für unsere Designs einzusetzen.“

Förderung

Das Projekt ANCONA wurde unter dem Förderkennzeichen 16ES021 im Förderprogramm IKT 2020 durch das Bundesministerium für Bildung und Forschung (BMBF) gefördert sowie durch die Industriepartner Infineon Technologies AG, Robert Bosch GmbH, Intel AG sowie Mentor Graphics GmbH unterstützt.

Zugehörige Inhalte

Projekt

ANCONA

Die erarbeiteten rechnergestützten Verifikationsmethoden beschleunigen die Entwicklung von Industrie-4.0-Anwendungen.

Veranstaltung,

DDECS 2019

IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems

Veranstaltung,

edaBarCamp -- may the 4th be with you!

Originating from our PhD meetings in a german research project, we gained the idea of starting an open research meeting based on the barcamp-concept.

Veranstaltung,

SMACD 2018

Vortrag auf der 15th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design

Kontakt

Kontakt

Dipl.-Hdl. Dipl.-Des. Beate Hövelmans

Leiterin Unternehmenskommunikation

beate.hoevelmans(at)imms.de+49 (0) 3677 874 93 13

Beate Hövelmans ist verantwortlich für die Text- und Bildredaktion dieser Webseite, für die Social-Media-Präsenz des IMMS auf LinkedIn und YouTube, die Jahresberichte, für die Pressearbeit mit Regional- und Fachmedien und weitere Kommunikationsformate des IMMS. Sie stellt Ihnen Texte, Bilder und Videomaterial für Ihre Berichterstattung zum IMMS bereit, vermittelt Kontakte für Interviews und ist Ansprechpartnerin für Veranstaltungen.