On evaluating the new methods, IMMS' industrial partner Melexis was able to identify the problematic points in three circuits in a very short time. Left: Dr. Dirk Nuernbergk (Melexis); right: Georg Gläser (IMMS). Photograph: IMMS.

# Motivation: New ways of designing faultless complex systems fast for the fourth industrial revolution

At the basis of all the smart systems which can function as part of the Internet of Things and of all the high performance applications needed in Industry 4.0 lies the technology contained in complex, highly integrated micro-electronic chips. System-on-Chip (SoC) technology comprises numerous elements and functions, both analogue and digital, into the narrowest of space, crowding together sensors, actuators and signal processing. Any errors in the design of the integrated circuits may impact on turnover to the tune of several hundred million dollars. They can cause costly downtime and, far worse, highly expensive product recall, repair and replacement. In order to keep such risks to a minimum, designers strive to recognise any faults as early as possible in the design process. In the context of Industry 4.0, also known as the fourth Industrial revolution, there is a further imperative: to design yet smarter and thus even more complex systems to meet new demands. Research is focussing on the development of many new system components for the future. How these will interact with current methods can as yet only be tested in experimental setups.

More on

ANCONA at

www.imms.de.

Annual Report

IMMS 2017

In anticipation, the ANCONA project partners have been working on computer-aided procedures which will provide reliable testing of complex systems even at the design stage and prove their functionality. These procedures are intended to simplify and significantly accelerate the design process for integrated circuits. They will boost in-> INSPECT novation potential and give their user a competitive edge. The specific development focus of IMMS has been on design methods which will, among other things, integrate parasitic coupling into system models and enable the coupling phenomena to be > in-ovo efficiently simulated. Three of these methods are presented here.

#### The IMMS solutions

# Why are new methods needed and what is the concept? Top-down design and bottom-up verification - a survey

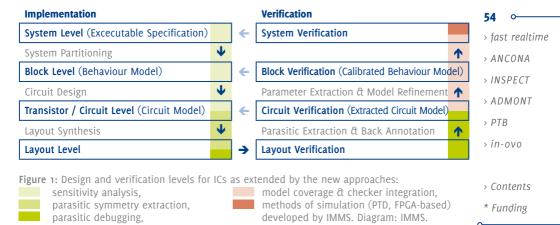

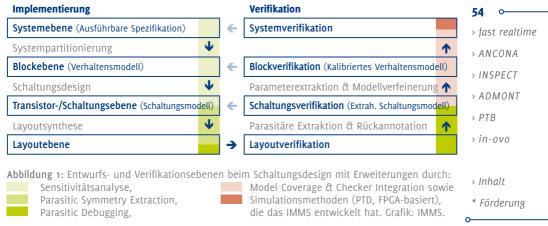

The design of integrated circuits usually begins at the systems level, as shown in Figure 1. It is here that function blocks are combined. Circuits are created within these components that will provide the desired function, amplification for example. And it is after this design stage that the functionality and electrical properties of the blocks are verified by means of simulation. If this stage goes well, a layout is designed to serve as template for the chip manufacturer, with such components as transistors and resistances positioned and linked by metallic connections.

New effects arise from the layout selected for these elements. There may, for example, be crosstalk between neighbouring connections which is caused by parasitics. Such physical effects, quite unrelated to the desired function, mean that the circuit must be verified anew. Usually, the layout has to go through further optimisation stages because of these effects. It is here that the first two methods presented in this article are helpful: parasitic impact analysis and symmetry analysis. Using symmetry analysis, it is possible that optimisation potential will show up even before the layout takes place. Impact analysis is a way of looking at existing layouts to decide on promising sites where improvements could be brought in. These methods thus considerably shorten layout optimisation time.

When correct functionality has been assured, the system can be tested stage by stage in ever larger function groups. If on the large scale there is a need not only • for the functions themselves but for monitoring of operating conditions, extremely accurate simulation at a low level of abstraction will usually be necessary, i.e. taking

> fast realtime

> ANCONA

53

> ADMONT

> PTB

> Contents \* Funding

More on ASIC developments:

www.imms.de.

**Annual Report IMMS 2017**

much time and computation. It is here that the third method comes in: in it, data on permitted operational conditions for individual function blocks is automatically extracted. It is then possible to integrate this data into more abstract models that will speed up simulation and at the same time provide security during subsequent operation later.

### Parasitic impact analysis

### Diagnosis and manual management of parasitics wearisome to impossible

Parasitic coupling due to the layout can be devastating to the function of a circuit and its electrical properties. This may result in high impact on stability, with other circuit elements disrupted or systematic errors developing which shift the set zero point, leading to offsets and thus to inaccuracy.

See "Impact Rating of Layout Parasitics ...": www.imms.de

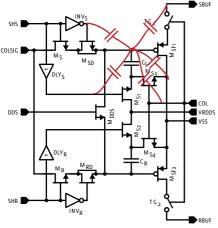

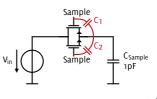

IMMS has applied and tested each of the new approaches in the case of specific chip development. In one case, the circuit shown in Figure 2 from the ADMONT project was subjected to parasitic impact analysis. This sampling circuit is used in a highly sensitive image sensor for fluorescence imaging. The accuracy of the circuit block is thus crucial to the chip function and it lies within the target range of <5mV. This value has to be as close as possible to zero. When the circuit was simulated, a negligible offset was revealed (<1mV). However, after layout, simulation with parasitics showed a significantly higher offset (>10mV) which would be excessive for the fluorescence chip.

Existing tools reveal the problem but are unable to identify the parasitic elements leading to the error.

It is, of course, physically possible for a designer to modify a circuit affected by parasitics manually and to investigate individual coupling effects. Such elements, however, typically run into the hundreds up to a thousand, which makes the approach rather less than practicable and at the same time requires deep knowledge of the circuit.

> fast realtime

> ANCONA

> INSPECT

> ADMONT

> PTB > in-ovo

> Contents

\* Funding

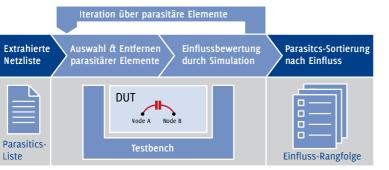

### A program to find and evaluate critical parasitics automatically

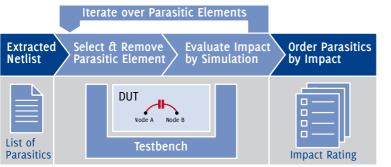

IMMS has created a program that enables these manual modifications to be automated and, at the same time, enables the circuit simulator to be used for evaluation of the modification that has taken place automatically. This is how the algorithm shown in Figure 3 was put into practice: each parasitic element is separated from the circuit in turn and a simulation run is started to determine the electrical properties. The result is a list allocating to each element its influence on the circuit. With the list, identification of the parasitic elements which will have a negative effect on the properties is simple. The number of simulations required is, however, huge: the simulation for evaluation purposes has to take place in respect of every single parasitic element.

To reduce this huge amount of simulation work, the algorithm was further improved. Instead of individual parasitic elements, all electrical couplings emanating from each circuit node can be examined. As there are far fewer nodes than parasitic elements, simulation is then much speedier.

Figure 3:

Impact analysis procedure.

Diagram: IMMS.

The layout of the fluorescence chip was improved, with absolute exactitude.

56

> in-ovo

> Contents

\* Funding

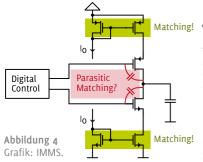

A It is the state of the art to set symmetry conditions for transistors, for instance in the case of current mirrors (highlighted in green).

For the parasitics (marked in red) there is to date no such method available.

###

symmetrical, they eliminate

systematic errors.

Sample

# Symmetry analysis

### Symmetry can compensate for errors - also in the case of parasitics

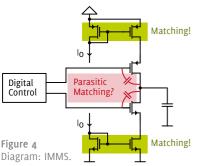

Symmetry is one of nature's basic concepts and one of technology's, too, which is also relevant for integrated circuits. Symmetry is exploited particularly at the layout stage to ensure components behave similarly in the presence of process variation. One instance is always to lay out current mirror circuits in symmetrical patterns. These symmetry conditions can be set in the circuit diagram even before layout, as shown in Figure 4.

Symmetry at a Glance ...":

See "Parasitic

www.imms.de

However, there has so far been no way of applying such conditions to parasitic elements, which may well cause systematic deviation in, for instance, sampling-and-hold circuits. One of these is shown in Figure 4. If the coupling currents of the circuit signals marked in red are equal to the output signal, the couplings compensate for each other and there will be no systematic error.

# New acceptance regions concept means symmetry extraction possible for parasitic elements

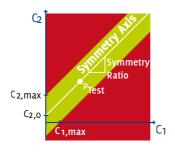

A method and also a tool prototype have been developed at IMMS from this principle within the ANCONA project. With the method it is possible to identify later symmetry conditions for parasitics in the layout before the actual layout takes place. The basis is the idea of acceptance regions, as shown in Figure 5. An acceptance region is a section of an area of parameters in which a particular circuit will work without error, i.e. within the specified tolerances.

Annual Report

MS GmbH. All rights reserved. Reproduction and publication only with express permission of IMMS

- Figure 6:

- Shape of acceptance region for symmetry condition.

- Diagram: IMMS.

- > fast realtime

- > ANCONA

- > INSPECT

- > ADMONT > PTB

- > in-ovo

### Acceptance regions – example

For example, in the case of the fluorescence chip described above, the specification is as follows: the output voltage is permitted to vary from the input voltage at the moment of sampling by only 5mV. If the parameters of parasitics  $C_1$  and  $C_2$  now vary, a picture will emerge as in Figure 6: the symmetry condition produces an acceptance corridor which lies within the specified area. Within this corridor, the capacity can vary without affecting the behaviour of the circuit. This shape of acceptance region is typical of symmetry conditions. It can be represented by means of three values: two of these are the two intersections with the axes  $C_1$ , max and  $C_2$ , max}, the third is the slope of the axis of symmetry (the relation between the capacities).

# Example of symmetry conditions

If the acceptance regions for all possible parasitics are investigated, symmetry conditions can be identified. To do so requires determining the maximum values of the capacities which can be tolerated, i.e. the intersections between the acceptance regions and the coordinate axes. To test whether a symmetry condition is contained in the overall parameter area under observation, a point along the axis of symmetry is selected. If the circuit behaviour is correct for this combination of parameters, i.e. if the point is found to lie in the "green region", a condition of symmetry has been shown.

Following this method does, however, require very many simulation runs. Their number can be greatly reduced by additional heuristic and plausibility tests. In collaboration with the ADMONT project, a circuit from an imager was investigated (see Figure 2). The analysis took six hours of simulation and produced more than 200 conditions of symmetry. The knowledge gained brought deeper understanding of the parasitics arising and can now be used for optimisation of the layout.

ContentsFunding

> ANCONA

> INSPECT

> ADMONT

> PTB

> in-ovo

Contents\* Funding

False positives in verification mean wearisome simulation and manual correction

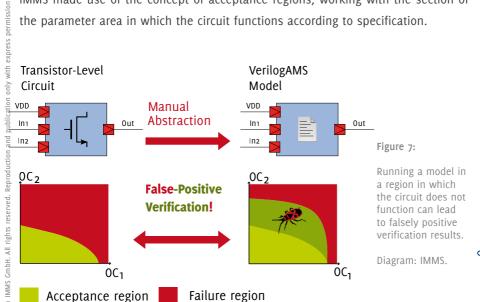

"The verification of a system tells you only as much as the models you use." Up to now there has been the possibility that positive verification of a design with purely functional models might turn out to be false and require validation by additional costly simulations.

This state of affairs is shown in Figure 7: if a model is run as in this case with too low a supply voltage, i.e. in a region in which the circuit would not function in practice, and yet produces a correct result, the verification is not reliable. An example of the situation is passive RFID tags which obtain their energy from the electromagnetic field, thus being subject to operating conditions which constantly vary.

To avoid this, it has been necessary so far to enter additional test conditions into the model manually or to carry out additional, time-consuming simulations.

There has to date been no way of generating the test conditions automatically for analog/mixed signal systems and entering them into existing models. For this reason IMMS made use of the concept of acceptance regions, working with the section of the parameter area in which the circuit functions according to specification.

See "There is a limit to everything ...":

www.imms.de

How do the test conditions and acceptance regions get into the model automatically?

> fast realtime

> ANCONA

59

> INSPECT

> ADMONT

> PTB > in-ovo

> Contents \* Funding

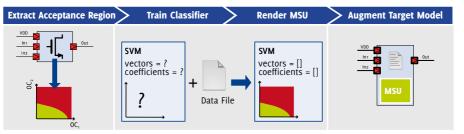

Quality before quantity

For the acceptance region to be integrated into a model, a suitable method of representation must first be found that can be visually represented in the IC design environment. As in industry, the Cadence AMS designer system is used. With this program, for instance, VerilogAMS models can be simulated. The decision as to whether the current environmental conditions are within or outside the acceptance region is a matter of classification. Because of the high flexibility, the choice of classifier falls on an SVM (support vector machine), which is a mathematical classification procedure. A method of automatically representing the classifiers in VerilogAMS models has been developed at IMMS.

### Automatically generated test condition observes and acts

As explained above, an SVM is used to represent the acceptance region. This classifier forms the core of an automatically generated test condition such as is shown in Figure 8. This unit contains not only the classifier. One other item is observer modules for purposes of monitoring the environment within the simulation. Another www.imms.de item is actuator modules for purposes of reacting to departure from the applicable operating area, for instance if a warning message is given or the system behaviour changes.

See "Knowing your A/MS System's Limit ...":

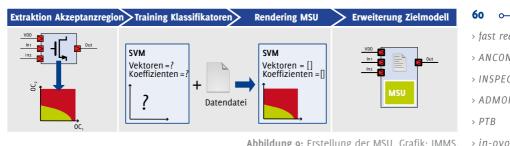

Now, thanks to a tool created by IMMS, the generation and integration of this test condition can be fully automated. New blocks are entered into the existing model, connecting leads are disconnected and connected anew. The process is shown in Figure 9. After the acceptance region for the circuit has been established, the classifier is trained and then transferred into VerilogAMS. This process entails combining the structure shown above, with its observer sensors and actuators, and integrating it into the existing model.

Figure 8:

Structure of the Model Safe-Guard Unit. Diagram: IMMS.

Figure 9: Creation of the MSU. Diagram: IMMS.

### > fast realtime

- > ANCONA

- > INSPECT > ADMONT

- > PTB > in-ovo

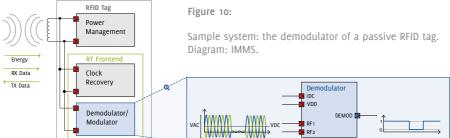

Passive RFID chip as example - tool cuts simulation time

Among the things IMMS develops in the ADMONT project are passive RFID frontends. It is essential to test these with reference to varying operating conditions because the power supply of the system components is constantly changing with changes in the field situation. The demodulator block from Figure 10 is an example. It obtains its data signal from the magnetic field in order to achieve communication with the tag.

During verification it became clear that simple functional modelling without reference to the environmental conditions is inadequate. There is a representation of this in Figure 11, with supply voltage VDD, equivalent value VDC and amplitude VAC of the input signal: the circuit will function properly in the green area but there will be interruptions to function in the red areas. On comparing the acceptance regions for the model (b) and the circuit (a), it will be seen that the model functions correctly even at VDD=0, i.e. with no voltage supply at all.

This can result in a falsely positive verification. So a test condition was created following the method described above and integrated into the system. The whole process took approx. 10 hours and produced an extended model of the demodulator which it is possible to simulate 100 times faster than the circuit can be.

Comparing the acceptance regions from Figure 11 (a) with the extended model (c) reveals that the acceptance regions match. Using a procedure also developed in the context of ANCONA, it has been proven that the risk of false positives in verification is almost completely excluded by this means.

> Contents

\* Funding

Other RFID solutions in the ADMONT specialist article.

More on ASIC developments: www.imms.de.

acceptance regions with and without MSU.

Diagram: IMMS.

### **Future prospects**

At the "14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design" (SMACD 2017) in June 2017, IMMS and its research partners were named competition runner-up for their contribution."Automated Generation of System-Level AMS Operating Condition Checks: Your Model's Insurance Policy". Before that, IMMS received two "Best Paper" awards at international conferences in 2016 and 2015: FDL (Forum on Specification & Design Languages). And by the end of 2017, the results from AN-CONA had been published in sixteen papers, among which eight peer-reviewed publications, nine lectures, four specialist posters and two book chapters.

> fast realtime

just reutiline

> ANCONA > INSPECT

> ADMONT

> PTB

> in-ovo

> Contents

\* Funding

For Fig. 11a

see "Comparing

Apples and

Oranges: ...":

www.imms.de

IMMS contributed crucial building blocks to the project in support of the aims: to ensure the reliability of the design of today's microelectronic systems. IMMS incorporated the new-style verification method into its research projects as an enhancement of the quality of designs made in those projects. Knowledge gained from this has been fed back into optimisation of the new method. IMMS has so far used the new methods for three chip developments in the ADMONT\* and RoMulus\* projects. Melexis, a long-standing industrial partner, was also able to identify the problem areas of three circuits in a very short time. It is intended that all the experience gained will be employed in the further development of the method in coming EDA projects.

More on

ANCONA at

www.imms.de.

Contact person: Georg Gläser, M.A., georg.glaeser@imms.de

The ANCONA project was funded by the BMBF (Federal German Ministry of Education and Research) in the IKT 2020 programme (funding reference 16ES021) and is also supported by industrial partners, Infineon Technologies AG, Robert Bosch GmbH, Intel AG and Mentor Graphics GmbH.

SPONSORED BY THE

Annual Report

IMMS 2017

Der Industriepartner Melexis konnte mit den Methoden des IMMS in kürzester Zeit die Problemstellen dreier Schaltungen identifizieren. Links im Bild: Dr.-Ing. Dirk Nuernbergk (Melexis); rechts: Georg Gläser (IMMS). Foto: IMMS.

# Motivation: Neue Methoden für schnelle und fehlerfreie Entwürfe komplexer Industrie-4.o-Lösungen

Für intelligente, im "Internet der Dinge" agierende Systeme und hochleistungsfähige Industrie-4.o-Anwendungen sind komplexe, hochintegrierte Mikroelektronik-Chips die technologische Basis. Solche SoCs (System-on-Chip) vereinen auf engstem Raum zahlreiche analoge und digitale Elemente und Funktionen wie Sensorik, Signalverarbeitung und Aktorik. Designfehler in integrierten Schaltungen können Umsatzeinbußen von mehreren hundert Mio. Dollar durch Produktionsausfälle verursachen und darüber hinaus weitaus höhere Kosten für Rückrufe, Reparaturen und Ersatzleistungen nach sich ziehen. Daher ist man bestrebt, Designfehler möglichst früh im Entwurfsprozess festzustellen und derartige Risiken zu minimieren. Darüber hinaus sollen für die neuen Anforderungen im Industrie-4.o-Kontext intelligentere und damit komplexere Systeme entstehen. Für diese werden künftig zahlreiche neue Systemkomponenten erforscht und entwickelt, deren Zusammenspiel mit den gängigen Methoden meist erst im Versuchsaufbau getestet werden kann.

Mehr zu

ANCONA auf

www.imms.de.

Jahresbericht

IMMS 2017

Daher haben die Projektpartner in ANCONA rechnergestützte Verfahren erarbeitet, um die korrekte Funktion dieser Systeme schon während des Entwurfs zuverlässig nachzuweisen. Das soll künftig das Design integrierter Schaltungen erleichtern und deutlich beschleunigen, somit Innovationspotentiale heben und zu Wettbewerbs-

> ANCONA

53

> INSPECT

> fast realtime

> ADMONT

> PTB

> in-ovo

> Inhalt \* Förderung

### Lösungen des IMMS

# Wozu neue Methoden und wo setzen sie an? Ein Überblick zu "top-down design" und "bottom-up verification"

Der Entwurf integrierter Schaltungen beginnt meist auf Systemebene (vgl. Abb. 1), auf der Funktionsblöcke kombiniert werden. In diesen Komponenten werden Schaltungen erstellt, die die gewünschte Funktion realisieren, wie z.B. eine Verstärkung. Nach diesem Entwurfsschritt werden die Funktionalität und die elektrischen Eigenschaften dieser Blöcke in Simulationen verifiziert. Ist dieser Schritt erfolgreich, so wird ein Layout erstellt, das der Bauplan für den Chiphersteller ist: Hier werden die Bauelemente, wie z.B. Transistoren und Widerstände, platziert und mittels Metallleitungen miteinander verbunden.

Durch die Anordnung dieser Elemente kann es jedoch zu neuen Effekten kommen, wie z.B. zum Übersprechen durch nebeneinanderliegende Leitungen, was durch parasitäre Kapazitäten verursacht wird. Aufgrund solcher physikalischen Effekte, die

Entwicklungen: www.imms.de.

Mehr zu ASIC-

nicht mit der gewünschten Funktion zusammenhängen, muss die Schaltung erneut verifiziert werden. Meist führen die Effekte dazu, dass das Layout in weiteren Schritten optimiert werden muss. Hier sind die ersten beiden vorgestellten Methoden, die "Parasitic-Impact-Analyse" und die "Symmetrieanalyse" hilfreich: Mit der Symmetrieanalyse können Optimierungspotentiale schon vor dem eigentlichen Layout aufgezeigt werden. Mit der Impact-Analyse werden vorhandene Layouts betrachtet, um einen vielversprechenden Angriffspunkt für die Verbesserungen zu bestimmen. Der aufwendige Prozess der Layoutoptimierung kann so stark verkürzt werden.

Nachdem die korrekte Funktion sichergestellt wurde, kann das System schrittwei- o se in immer größeren Funktionsgruppen geprüft werden. Wenn dabei neben der Funktionalität auch die Betriebsbedingungen überwacht werden sollen, ist meist

eine sehr detailtreue Simulation auf niedriger Abstraktionsebene notwendig, d.h. mit aufwendigen und zeitintensiven Lösungsverfahren. An dieser Stelle setzt die dritte vorgestellte Methode an: Mit dieser werden Informationen über erlaubte Betriebsbedingungen einzelner Funktionsblöcke automatisch extrahiert. Diese Informationen werden dann in abstraktere Modelle eingearbeitet, mit denen Simulationen stark beschleunigt und gleichzeitig die Betriebsbedingungen abgesichert werden.

### Parasitic-Impact-Analyse

# Parasiten - Diagnose und manuelle Therapie aufwendig bis unmöglich

Parameter einer Schaltung erheblich stören. So kann es dazu kommen, dass die Stabilität beeinträchtigt wird, in anderen Schaltungsteilen Störungen durch Kopplungen verursachen oder systematische Fehler eingefügt werden, die den Nullpunkt verschieben und zu sog. Offsets und damit Ungenauigkeiten führen können.

Die parasitären Kopplungen aus dem Layout können die Funktion und elektrischen

Das IMMS hat jeden der neuen Methoden-Ansätze an konkreten Chip-Entwicklungen überprüft. Unter anderem wurde die in Abbildung 2 gezeigte Schaltung aus dem Projekt ADMONT einer Parasitic-Impact-Analyse unterzogen. Diese Abtastschaltung wird in einem höchst empfindlichen Bildsensor für Fluoreszenz-Imaging eingesetzt. Die Genauigkeit dieses Blocks ist dabei entscheidend für die Funktion des Chips und liegt im Zielbereich <5mV. Je kleiner der Wert, desto besser. Die Simulation der Schaltung zeigte einen vernachlässigbar kleinen Offset (<1mV). Nach dem Layout war dieser jedoch in der Simulation mit parasitären Elementen signifikant größer

(>10mV) und damit für den Fluoreszenz-Chip zu groß.

Vgl. "Impact

Rating of Layout

Parasitics ...":

www.imms.de

IMMS GmbH. Alle Rechte sind vorbehalten. Vervielfältigung

Abbildung 2: Abtastschaltung eines Fluoreszenz-Imagers aus dem Projekt ADMONT. Einige parasitäre Kopplungen sind rot eingezeichnet. Grafik: IMMS. Bestehende Werkzeuge zeigen dieses Problem auf, ohne jedoch die parasitären Elemente zu identifizieren, welche den Fehler verursachen.

Ein Designer kann durchaus eine Schaltung mit parasitären Elementen manuell modifizieren und die Auswirkung einzelner Kopplungen untersuchen. Da jedoch die Anzahl dieser Elemente typischerweise bei mehreren hundert bis tausend liegt, ist dieser Ansatz wenig praktikabel und erfordert ein tiefes Verständnis der Schaltung.

> fast realtime

55

> ANCONA

> INSPECT > ADMONT

> PTB

> in-ovo

> Inhalt

\* Förderung

### Programm findet und bewertet automatisch kritische parasitäre Elemente

Das IMMS hat ein Programm erstellt, mit dem es möglich ist, diese manuellen Anpassungen zu automatisieren und gleichzeitig den Schaltungssimulator zur Auswertung der Modifikation zu verwenden. Der in Abbildung 3 gezeigte Algorithmus wurde wie folgt realisiert: Nacheinander wird jedes parasitäre Element aus der Schaltung entfernt und ein Simulationslauf zur Bewertung der elektrischen Eigenschaften gestartet. So entsteht eine Liste, die jedem Element seinen Einfluss auf die Schaltung zuordnet. Hier können die parasitären Elemente, die zur Verschlechterung der Eigenschaften führen, leicht identifiziert werden. Dennoch ist die Anzahl der notwendigen Simulationen extrem hoch: Für jedes parasitäre Element muss eine Simulation zur Bewertung ausgeführt werden.

Um diesen Simulationsaufwand zu reduzieren, wurde der Algorithmus weiter verbessert. Anstatt die Betrachtung auf einzelne parasitäre Elemente zu beziehen, können ebenso alle von einem Schaltungsknoten ausgehenden Kopplungen betrachtet

Abbildung 3:

Ablauf der Impact-Analyse.

Grafik: IMMS. •

werden. Da die Anzahl der Knoten viel kleiner ist als die der parasitären Elemente, ist hier der Simulationsaufwand viel geringer. Für die in Abbildung 2 gezeigte Schaltung mussten 450 Kopplungen, aber nur etwa 20 Knoten untersucht werden. Der Simulationsaufwand konnte durch die Verbesserung also um den Faktor 20 reduziert werden. Fünf Schwachstellen wurden so in zehn Minuten gefunden und das Layout des Fluoreszenz-Chips punktgenau verbessert.

Matching! ◀ Symmetriebedingungen für Transistoren, z.B. in den grün markierten Stromspiegeln, sind Stand der Technik.

> Für parasitäre Elemente (rot) existiert noch keine Methode dieser Art.

▲ Eine einfache Abtast-Halte-Schaltung. Rot markiert sind parasitäre Koppelkapazitäten. Sind sie symmetrisch, heben sie systematische Fehler auf.

### > fast realtime

- > ANCONA

56

- > INSPECT

- > ADMONT

- > PTB

- > in-ovo

- > Inhalt \* Förderung

Vgl. "Parasitic

Symmetry at a

www.imms.de

Glance ... ":

# Symmetrieanalyse

## Symmetrien können Fehler kompensieren - auch für parasitäre Elemente

Symmetrie ist eines der fundamentalen Konzepte der Natur und Technik. So auch im Entwurf integrierter Schaltungen: Insbesondere im Layout werden Symmetrien ausgenutzt, um gleiches Verhalten von Bauelementen in Gegenwart von Prozessvarianzen zu gewährleisten. So werden z.B. Stromspiegelschaltungen immer in symmetrischen Mustern platziert. Diese Symmetriebedingungen können schon vor dem Layout im Schaltplan angegeben werden, wie in Abbildung 4 (rechts) dargestellt.

Jedoch ist es bisher nicht möglich, derartige Bedingungen für parasitäre Elemente anzugeben. Diese können z.B. bei Abtast-/Halte-Schaltungen zu systematischen Abweichungen führen. Eine solche Schaltung ist in Abbildung 4 (links) dargestellt. Sind die rot markierten Koppelkapazitäten von den Schaltersignalen auf das Ausgangssignal gleich, so kompensieren sich die Kopplungen gegenseitig und es entsteht kein systematischer Fehler.

Neues Konzept der Akzeptanzregionen ermöglicht Symmetrieextraktion für parasitäre Elemente

Im Projekt ANCONA wurde am IMMS aus diesem Prinzip eine Methode und auch ein Prototyp für ein Werkzeug entwickelt, mit der es schon vor dem eigentlichen Layout möglich ist, spätere Symmetriebedingungen parasitärer Elemente im Layout zu

**Tahresbericht IMMS 2017**

Akzeptanz-

region (Schaltung

**Fehlerregion**

Parameterraum

Abbildung 6:

bedingung.

Grafik: IMMS.

einer Symmetrie-

> INSPECT Form der Akzeptanzregion

> ADMONT

> ANCONA

> fast realtime

> PTB > in-ovo

identifizieren. Diese Methode basiert auf dem Konzept der Akzeptanzregionen, wie in Abbildung 5 dargestellt. Eine Akzeptanzregion ist ein Teil des Parameterraums, in dem eine gegebene Schaltung fehlerfrei, d.h. im Rahmen der Spezifikation arbeitet.

> Inhalt \* Förderung

### Akzeptanzregionen - Beispiel

Für das zuvor gezeigte Beispiel des Fluoreszenz-Chips ist die Spezifikation beispielsweise: Die Ausgangsspannung soll von der Eingangsspannung im Abtastzeitpunkt nur um 5mV abweichen. Werden nun die Parameter der parasitären Kapazitäten C<sub>1</sub> und C2 variiert, ergibt sich ein Bild wie in Abbildung 6: Die Symmetriebedingung erzeugt einen Akzeptanz-Korridor im Parameterraum. In diesem Bereich können die Kapazitäten beliebige Werte annehmen, ohne das Schaltungsverhalten zu beeinträchtigen. Diese Form der Akzeptanzregion ist typisch für Symmetriebedingungen. Sie kann durch drei Größen erfasst werden: Einerseits durch die beiden Schnittpunkte mit den Koordinatenachsen C<sub>1, max</sub> und und C<sub>{2, max}</sub>, andererseits durch den Anstieg der Symmetrieachse (das Verhältnis der Kapazitäten).

### Symmetriebedingungen - Beispiel

Untersucht man die Akzeptanzgebiete aller möglichen parasitären Kapazitäten, lassen sich Symmetriebedingungen identifizieren. Dazu ist es notwendig, die maximal tolerierbaren Werte der Kapazitäten zu bestimmen, also die Schnittpunkte der Akzeptanzbereiche mit den Koordinatenachsen. Um zu testen, ob der betrachtete Parameterraum eine Symmetriebedingung enthält, wird ein Punkt entlang der Symmetrieachse ausgewählt. Ist das Verhalten der Schaltung für diese Parameterkombination korrekt, d.h. der Punkt liegt im "grünen Bereich", ist die Symmetriebedingung nachgewiesen.

Diese Methode erfordert jedoch eine hohe Anzahl an Simulationsläufen. Diese kann durch zusätzliche Heuristiken und Plausibilitätstests stark reduziert werden. In Zusammenarbeit mit dem Projekt ADMONT wurde eine Schaltung aus einem Bildsen-

**Tahresbericht IMMS 2017**

Model Safe-Guard Unit – das Ende falsch-positiver Verifikationsergebnisse durch Betriebsbedingungen

Falsch-positive Verifikationen ziehen zeitaufwändige Simulationen und Handarbeit nach sich

"Die Verifikation eines Systems ist nur so aussagekräftig wie die verwendeten Modelle." Bislang konnte es vorkommen, dass sich eine positive Verifikation eines Entwurfs mit rein funktionalen Modellen als falsch herausstellte und durch zusätzliche Simulationen abgesichert werden musste.

Dieses Problem eines falsch-positiven Ergebnisses ist in Abbildung 7 dargestellt: Wenn ein Modell wie hier mit zu kleiner Versorgungsspannung betrieben wird, also in einem Bereich, in dem die realisierte Schaltung nicht funktionieren würde, und dennoch ein korrektes Ergebnis liefert, ist das Verifikationsergebnis nicht zuverlässig. Dieser Effekt kann z.B. bei passiven RFID-Tags auftreten, die ihre Energie aus dem elektromagnetischen Feld gewinnen und deren Betriebsbedingungen sich deshalb ständig ändern.

Deshalb müssen bisher entweder manuell zusätzliche Prüfbedingungen in das Modell eingefügt oder zusätzliche, zeitaufwendige Simulationen durchgeführt werden.

Schaltung VerilogAMS-Transistorebene Modell VDD Manuelle VDD Abstraktion ln 1 0ut ln 1 0ut Abbildung 7: GmbH. Alle Rechte sind vorbehalten. Wird ein Modell 0C2 0C2 in einem Bereich **Falsch-positive** betrieben, in dem Verifikation! die Schaltung nicht mehr funktioniert, kann es zu falschpositiven Verifikationsergebnissen  $0C_1$ 0C<sub>1</sub> kommen. Akzeptanzregion **Fehlerregion** Grafik: IMMS.

> fast realtime

> ANCONA

58

> INSPECT

> ADMONT

> PTB

> in-ovo

> Inhalt

\* Förderung

Vgl. "There is a limit to everything ...":

www.imms.de

Für Analog/Mixed-Signal-Systeme existiert bisher kein Ansatz, um solche Prüfbedingungen automatisch zu erzeugen und in bestehende Modelle einzufügen. Daher wurde am IMMS auch hierfür das Konzept der Akzeptanzregionen angewendet, d.h. mit dem Teil des Parameterraums gearbeitet, in dem die Schaltung gemäß der Spezifikation funktioniert.

> fast realtime

> ANCONA

59

> INSPECT > ADMONT

> PTB > in-ovo

Wie kommen Prüfbedingungen und Akzeptanzregionen automatisch ins Modell?

> Inhalt

\* Förderung

Vgl. "Knowing your A/MS System's Limit ...": www.imms.de

Klasse statt Masse

Um diese Akzeptanzregion in ein Modell integrieren zu können, muss zunächst eine passende Repräsentation gefunden werden, die in der Entwurfsumgebung für integrierte Schaltungen abgebildet werden kann. Wie in der Industrie kommt hier das Programm AMS-Designer von Cadence zum Einsatz. Damit können z.B. VerilogAMS Modelle simuliert werden. Die Entscheidung, ob die aktuellen Umgebungsbedingungen zur Akzeptanzregion gehören oder nicht, ist ein Klassifikationsproblem. Aufgrund der hohen Flexibilität bieten sich hier Klassifikatoren auf Basis einer Support Vector Machine (SVM) an, einem mathematischen Verfahren zur Klassifikation. Am IMMS wurde eine Methode entwickelt, diese Klassifikatoren automatisiert in Verilog-AMS-Modellen abzubilden.

Automatisch erzeugte Prüfbedingung beobachtet und agiert

Wie zuvor erläutert, wird eine SVM dazu verwendet, die Akzeptanzregion abzubilden. Dieser Klassifikator bildet den Kern einer automatisch erzeugten Prüfbedingung, wie sie in Abbildung 8 dargestellt ist. Neben dem Klassifikator enthält diese Einheit zum einen Sensormodule, um die Umgebung innerhalb der Simulation zu beobachten. Zum anderen enthält sie Aktormodule, um auf das Verlassen des gültigen Betriebsbereiches zu reagieren, z.B. mit Fehlermeldungen oder Veränderungen des Systemverhaltens. Die Erzeugung und Integration dieser Prüfbedingung kann dank eines vom IMMS erstellten Werkzeuges vollständig automatisiert werden. Im vorhandenen Modell werden dazu neue Blöcke eingefügt, Verbindungsleitungen aufgetrennt und

**Model Safe-Guard Unit (MSU)** Klassifi-Sensor kator (SVM) Sensor Aktor OC. 🛊 Sensor

Abbildung 8:

Struktur der Model Safe-Guard Unit. Grafik: IMMS.

lahresbericht **IMMS 2017**

Energy

RX Data

**RFID Tag**

Management

RF Frontend

Power

Clock

Recovery

Demodulator/

Modulator

Abbildung 9: Erstellung der MSU. Grafik: IMMS.

neu verbunden. Der Prozess ist in Abbildung 9 dargestellt. Nachdem die Akzeptanzregion der Schaltung erkundet wurde, wird der Klassifikator trainiert und in Verilog-AMS überführt. Dabei wird die zuvor gezeigte Struktur mit Sensoren und Aktoren zusammengestellt und in das vorhandene Modell eingefügt.

> Mehr zu RFID-Lösungen im ADMONT-

**Fachartikel**

> fast realtime

> ANCONA

> INSPECT

> ADMONT

> PTB

> Inhalt

\* Förderung

### Beispiel passiver RFID-Chip - Tool schrumpft Simulationsaufwand

Im Projekt ADMONT werden am IMMS u.a. passive RFID-Sensor-Frontends entwickelt. Da sich hier z.B. die Versorgungsspannung der Systemkomponenten fortlaufend je nach Feldsituation ändern, müssen diese insbesondere im Hinblick auf Betriebsbedingungen untersucht werden. Als Beispiel dient hier der Demodulator-Block aus dem in Abbildung 10 dargestellten RFID-Tag. Dieser Block gewinnt das Datensignal aus dem magnetischen Feld zurück, um so eine Kommunikation mit dem Tag zu realisieren.

In der Verifikation zeigte sich, dass eine rein funktionale Modellierung ohne Rücksicht auf die Umgebungsbedingungen nicht ausreicht. Dies ist in Abbildung 11 für die Größen Versorgungsspannung VDD, Gleichwert VDC und Amplitude VAC des Eingangssignals dargestellt: In den grün markierten Bereichen ist die Schaltung funktionsfähig, in den roten Bereichen kommt es zu Funktionsstörungen. Der Vergleich der Akzeptanzbereiche von Modell (b) und Schaltung (a) zeigt, dass das Modell z.B. auch bei VDD=o, also ohne Versorgungsspannung, korrekt funktioniert. Hier kann es zu falschpositiven Verifikationsergebnissen kommen. Deshalb wurde mit der zuvor vorgestellten Methode eine Prüfbedingung erstellt und in das System eingewoben. Der gesam-

> te Prozess nahm etwa 10h in Anspruch und ergab ein erweitertes Modell des Demodulators, welches etwa 100 Mal schneller simuliert werden kann als die Schaltung. Abbildung 10: Beispielsystem:

Demodulator eines passiven RFID-Tags. Grafik: IMMS. Demodulator DEMOD

Mehr zu ASIC-Entwicklungen: www.imms.de.

lahresbericht **IMMS 2017**

**Abbildung 11:** Vergleich der Akzeptanzregionen von Schaltung und Modell mit und ohne MSU. Grafik: IMMS.

Der Vergleich der Akzeptanzbereiche aus Abbildung 11 (a) und dem erweiterten Modell (c) zeigt eine Übereinstimmung der Regionen. Mit einem ebenfalls in ANCONA entwickelten Verfahren konnte nachgewiesen werden, dass das Risiko einer Falsch-positiven Verifikation dadurch nahezu ausgeschlossen werden kann.

### Ausblick:

Gemeinsam mit Forschungspartnern wurde das Institut 2017 auf der "14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design" (SMACD 2017) in Tahormina, Italien, für den Beitrag "Automated Generation of System-Level AMS Operating Condition Checks: Your Model's Insurance Policy" als Competition Runner-up geehrt. Davor erhielt das IMMS zwei Best-Paper-

> fast realtime

> ANCONA

> INSPECT

> ADMONT > PTB

> in-ovo

> Inhalt

\* Förderung

Vgl. zu Abb.

11a "Comparing

Apples and

Oranges: ...":

www.imms.de

Mehr zu

ANCONA auf

www.imms.de.

Awards auf internationalen Konferenzen "Forum on Specification & Design Languages" (FDL) 2016 und 2015. Darüber hinaus wurden die Ergebnisse aus ANCONA bis Ende 2017 in sechzehn Beiträgen publiziert, darunter acht begutachtete Veröffentlichungen, neun Vorträge, vier Fachposter sowie zwei Buchkapitel. Das IMMS hat die neuen Methoden bislang für drei Chip-Entwicklungen in den Projekten ADMONT\* und RoMulus\* verwendet. Der langjährige Industriepartner Melexis konnte zudem in kürzester Zeit die Problemstellen dreier Schaltungen identifizieren. Die Methoden werden für wei-

tere ASIC-Entwicklungen des IMMS genutzt und sollen künftig ausgebaut werden.

Kontakt: Georg Gläser, M.Sc., georg.glaeser@imms.de

Das Projekt ANCONA wurde unter dem Förderkennzeichen 16ES021 im Förderprogramm IKT 2020 durch das Bundesministerium für Bildung und Forschung (BMBF) gefördert sowie durch die Industriepartner Infineon Technologies AG, Robert Bosch GmbH, Intel AG sowie Mentor Graphics GmbH unterstützt.

Bundesministerium für Bildung und Forschung

GEFÖRDERT VOM